Ang RISC V ay isang Instruction set architecture na binuo ng University of California, Berkeley. Ang konsepto ng RISC ay naudyukan ng katotohanan na ang karamihan sa mga tagubilin ng processor ay hindi ginagamit ng karamihan sa mga programa sa computer. Kaya, ang hindi kinakailangang decoding logic ay ginagamit sa loob ng mga disenyo ng mga processor , kumokonsumo ng mas maraming kapangyarihan pati na rin ang lugar. Upang paikliin ang set ng pagtuturo at upang mamuhunan nang higit pa sa loob ng mga mapagkukunan ng pagpaparehistro, ang RISC V processor ay ipinatupad.

Ang teknolohiyang ito ay napansin ng maraming tech giant at start-up dahil ito ay ganap na open source at libre. Karamihan sa mga uri ng processor ay available na may kasunduan sa lisensya, gayunpaman sa ganitong uri ng processor; kahit sino ay maaaring gumawa ng kanilang mga bagong disenyo ng processor. Kaya tinatalakay ng artikulong ito ang isang pangkalahatang-ideya ng isang RISC V processor - gumagana at ang mga aplikasyon nito.

Ano ang RISC V Processor?

Sa RISC V processor, ang terminong RISC ay kumakatawan sa 'reduced instruction set computer' na nagpapatupad ng ilang mga tagubilin sa computer samantalang ang 'V' ay kumakatawan sa ika-5 henerasyon. Ito ay isang open-source hardware ISA (instruction set architecture) batay sa itinatag na prinsipyo ng PANGANIB .

Kung ikukumpara sa iba pang mga disenyo ng ISA, ang ISA na ito ay magagamit sa isang open source na lisensya. Kaya, ang isang bilang ng mga kumpanya ng pagmamanupaktura ay nag-anunsyo at nagbigay din ng RISC-V hardware, na may mga open-source na operating system.

Isa itong bagong arkitektura at available sa bukas, hindi mahigpit at libreng mga lisensya. Ang processor na ito ay may malawak na suporta mula sa mga industriya ng paggawa ng chip at device. Kaya ito ay pangunahing idinisenyo upang malayang mapalawak at nako-customize na gamitin sa maraming mga application.

Kasaysayan ng RISC V

Ang RISC ay naimbento ni Prof. David Patterson noong 1980 sa Unibersidad ng California, Berkeley. Ang Prof. David kasama si Prof. John Hennessy ay nagsumite ng kanilang mga pagsisikap sa dalawang aklat na ang 'Computer Organization and Design' at 'Computer Architecture sa Stanford University. Kaya, natanggap nila ang ACM A.M. Turing award sa taong 2017.

Mula sa taong 1980 hanggang 2010 na taon, ang RISC fifth-generation development research ay sinimulan at sa wakas ay nakilala bilang RISC-V na binibigkas bilang risk five.

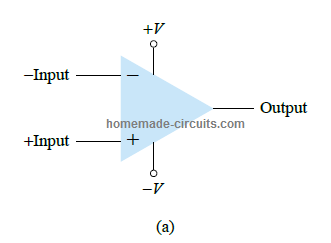

RISC V Arkitektura at Paggawa

Ang arkitektura ng RV12 RISC V ay ipinapakita sa ibaba. Ang RV12 ay lubos na nako-configure sa isang single-core na RV32I at RV64I na sumusunod sa RISC CPU na ginagamit sa mga naka-embed na field. Ang RV12 ay mula rin sa isang 32 o 64-bit na pamilya ng CPU depende sa pamantayang pang-industriya na set ng pagtuturo ng RISC-V.

Ang RV12 ay nagpapatupad lamang ng isang arkitektura ng Harvard para sa sabay-sabay na pag-access sa pagtuturo pati na rin ang memorya ng data. Kasama rin dito ang isang 6-stage na pipeline na tumutulong sa pag-optimize ng mga overlap sa pagitan ng execution pati na rin ang mga access sa memory upang mapabuti ang kahusayan. Pangunahing kasama sa arkitektura na ito ang Branch Prediction, Data Cache, Debug Unit, Instruction Cache, at opsyonal na Multiplier o Divider Units.

Ang mga pangunahing tampok ng RV12 RISC V ay kinabibilangan ng mga sumusunod.

- Ito ay isang set ng pagtuturo na pamantayan sa industriya.

- Na-parameter na may 32 o 64bit na data.

- Mayroon itong tumpak at mabilis na pagkagambala.

- Pinapayagan ng mga custom na tagubilin ang pagdaragdag ng mga proprietary hardware accelerators.

- Pagpapatupad ng solong cycle.

- Anim na yugto ng pipeline na may pag-optimize na nakatiklop.

- Suporta sa proteksyon ng memorya.

- Opsyonal o Parameterized na mga cache.

- Sobrang Parameterized.

- Maaaring pumili ang mga user ng 32/64-bit na data at Branch Prediction Unit.

- Maaaring pumili ang mga user ng mga tagubilin/data cache.

- Napipili ng user na istraktura, laki at arkitektura ng cache.

- Hardware Divider o Multiplier Support sa pamamagitan ng latency na tinukoy ng user.

- Ang arkitektura ng bus ay flexible na sumusuporta sa Wishbone at AHB.

- Ino-optimize ng disenyong ito ang kapangyarihan at laki.

- Ganap na naka-parameter ang disenyo na nagbibigay ng performance o power tradeoffs.

- Gated CLK na disenyo upang bawasan ang kapangyarihan.

- Suporta sa software ayon sa pamantayan ng Industriya.

- Simulator ng arkitektura.

- Ang Eclipse IDE ay ginagamit para sa Linux/ Windows.

Ang RISC V Execution Pipeline

Kabilang dito ang limang yugto tulad ng IF (instruction fetch), ID (instruction decode), EX (execute), MEM (memory access) at WB (register write-back).

Instruction Fetch

Sa yugto ng Instruction Fetch o IF, ang isang pagtuturo ay binabasa mula sa program counter (PC) at memory ng pagtuturo na ina-update sa susunod na pagtuturo.

Pagtuturo Pre-Decode

Kapag pinayagan ang RVC Support, ang yugto ng Instruction Pre-Decode ay magde-decode ng 16-bit-compressed na pagtuturo sa isang native na 32-bit na pagtuturo.

Decode ng Pagtuturo

Sa yugto ng Instruction Decode (ID), pinapayagan ang Register File at ang mga kontrol sa bypass ay napagpasyahan.

Ipatupad

Sa yugto ng Execute, ang resulta ay kinakalkula para sa isang ALU, DIV, MUL na pagtuturo, ang memorya na pinapayagan para sa isang Store o Load na pagtuturo, at ang mga branch at jump ay sinusukat laban sa kanilang inaasahang resulta.

Alaala

Sa yugtong ito ng Memorya, naa-access ang memorya sa pamamagitan ng pipeline. Tinitiyak ng pagsasama ng yugtong ito ang mataas na pagganap ng pipeline.

Sagutin ang sulat

Sa yugtong ito, ang resulta ng yugto ng Pagpapatupad ay nakasulat sa Register File.

Tagahula ng Sangay

Kasama sa processor na ito ang isang branch predictor unit o BPU na ginagamit upang mag-imbak ng nakaraang data upang gabayan ang RISC V processor sa pagpapasya kung ang isang partikular na branch ay kinuha o hindi-. Ang data ng predictor na ito ay naa-update lamang kapag naisakatuparan ang sangay.

Kasama sa unit na ito ang iba't ibang parameter na tumutukoy sa pag-uugali nito. Halimbawa, ang HAS_BPU ay ginagamit upang matukoy kung ang isang sangay ay hinuhulaan na ang isang yunit ay naroroon, ang BPU_GLOBAL_BITS ay tutukuyin kung gaano karaming mga nakaraang bit ang dapat gamitin at ang BPU_LOCAL_BITS ay tutukuyin kung gaano karami sa LSB ng program counter ang dapat gamitin. Ang kumbinasyon ng BPU_LOCAL_BITS at BPU_GLOBAL_BITS ay lilikha ng vector na pangunahing ginagamit upang tugunan ang Branch-Prediction-Table.

Data Cache

Ito ay pangunahing ginagamit upang pabilisin ang pag-access ng memorya ng data sa pamamagitan ng pag-buffer ng mga bagong na-access na lokasyon ng memorya. Ito ay may kakayahang pangasiwaan ang mga access sa kalahating salita, byte at salita kapag XLEN = 32 kung nasa kanilang sariling mga hangganan. May kakayahan din itong pangasiwaan ang mga access sa kalahating salita, byte, salita at dobleng salita kapag XLEN=64 kung nasa kanilang sariling mga hangganan.

Sa kabuuan ng isang cache miss, ang isang buong bloke ay maaaring isulat pabalik sa memorya, Kaya kung kinakailangan, isang bagong bloke ay maaaring mai-load sa cache. Ang Data Cache ay hindi pinagana sa pamamagitan ng pagtatakda ng DCACHE_SIZE sa zero. Pagkatapos nito, direktang naa-access ang mga lokasyon ng memorya sa pamamagitan ng Interface ng Data .

Cache ng Pagtuturo

Pangunahing ginagamit ito upang pabilisin ang pagkuha ng pagtuturo sa pamamagitan ng pag-buffer ng mga bagong kinuhang tagubilin. Ang cache na ito ay ginagamit upang kumuha ng isang parsela para sa bawat cycle sa anumang 16-bit na hangganan ngunit hindi sa isang bloke na hangganan. Sa buong cache miss, ang isang buong bloke ay maaaring mai-load mula sa memory ng pagtuturo. Ang pagsasaayos ng cache na ito ay maaaring gawin batay sa mga pangangailangan ng gumagamit. Ang laki ng cache, kapalit na algorithm, at haba ng block ay maaaring i-configure.

Idi-disable ang ikot ng pagtuturo sa pamamagitan ng Pagtatakda ng ICACHE_SIZE sa zero. Pagkatapos nito, ang mga parsela ay direktang kinukuha mula sa memorya sa pamamagitan ng Interface ng Pagtuturo.

Debug Unit

Ang Debug Unit ay magbibigay-daan sa Debug environment na huminto at suriin ang CPU. Ang mga pangunahing tampok nito ay Branch Tracing, Single Step Tracing hanggang sa 8- Hardware Breakpoints.

Magrehistro ng File

Dinisenyo ito na may 32 mga lokasyon ng rehistro mula X0 hanggang X31 kung saan ang X9 Register ay palaging zero. Kasama sa Register File ang 1- write port at 2- read port.

Nako-configure na Interface

Isa itong panlabas na interface kung saan sinusuportahan ng processor na ito ang iba't ibang panlabas na interface ng bus.

Paano Gumagana ang RISC V?

Ang RISC-V ay isang arkitektura ng set ng pagtuturo na nakaugat sa mga prinsipyo ng RISC (reduced instruction set computer). Ang processor na ito ay napaka-natatangi at rebolusyonaryo rin dahil ito ay isang libre, karaniwan, at open-source na ISA kung saan ang hardware ay maaaring mabuo, ang software ay maaaring i-port at ang mga processor ay maaaring idisenyo upang suportahan ito.

Pagkakaiba B/W RISC V Vs MIPS

Ang pagkakaiba sa pagitan ng RISC V at MIPS ay kinabibilangan ng mga sumusunod.

|

RISC V |

MIPS |

| Ang terminong RISC V ay kumakatawan sa Reduced Instruction Set Computer kung saan ang 'V' ay ang ikalimang henerasyon. | Ang terminong 'MIPS' ay nangangahulugang 'Million instructions per second'. |

| Pinapahintulutan lamang ng RISC-V ang mga tagagawa ng mas maliliit na device na magdisenyo ng hardware nang hindi nagbabayad. | Pinapayagan ng MIPS ang tagagawa na sukatin ang bilis ng processor sa pamamagitan ng pagbabayad dahil hindi ito libre. |

| MIPS ay mahusay na patay. | Ang RISC-V ay hindi mahusay na patay. |

| Ang processor na ito ay nagbibigay ng mga tagubilin sa sangay para sa paghahambing ng dalawang rehistro. | Ang MIPS ay nakadepende sa isang paghahambing na pagtuturo na nakakahanap ng isang rehistro sa 1 o 0 batay sa kung ang kaibahan ay totoo. |

| Ang ISA encoding scheme ay fixed at variable sa RISC V. | Ang ISA encoding scheme ay naayos sa MIPS |

| Ang laki ng set ng pagtuturo ay 16-bit o 32-bit o 64-bit o 128-bit. | Ang laki ng set ng pagtuturo ay 32-bit o 64-bit. |

| Mayroon itong 32 pangkalahatang layunin at floating point registers | Mayroon itong 31 pangkalahatang layunin at floating point na mga rehistro. |

| Mayroon itong 26-single at double precision floating point operations. | Mayroon itong 15-single at double precision floating point operations. |

Pagkakaiba B/W RISC V Vs ARM

Ang pagkakaiba sa pagitan ng RISC V Vs ARM ay kinabibilangan ng mga sumusunod.

|

RISC V |

BISO |

| Ang RISC-V ay open source, kaya hindi ito nangangailangan ng anumang lisensya. | Ang ARM ay isang closed source, kaya kailangan nito ng lisensya. |

| Ito ay isang bagong platform ng processor, kaya mayroong napakaliit na suporta para sa software at programming environment. | Ang ARM ay may napakalaking online na komunidad, na sumusuporta sa mga aklatan at istruktura upang tulungan ang mga target na taga-disenyo sa iba't ibang platform tulad ng mga microprocessor, microcontroller at mga server din. |

| Gumagamit ang RISC V-based chips ng 1 watt ng power. | Ang mga chip na nakabatay sa ARM ay gumagamit ng mas mababa sa 4 watts ng kapangyarihan. |

| Mayroon itong fixed at variable na ISA encoding system. | Mayroon itong nakapirming ISA encoding system. |

| Ang laki ng set ng pagtuturo ng RISC V ay mula 16-bit hanggang 128-bits. | Ang laki ng pagtuturo nito ay mula 16-bit hanggang 64-bits. |

| Kabilang dito ang 32 pangkalahatang layunin at mga rehistro ng floating point. | Kabilang dito ang 31 pangkalahatang layunin at mga rehistro ng floating point. |

| Mayroon itong 26-single precision floating point operations. | Mayroon itong 33-single precision floating point operations. |

| Mayroon itong 26-double precision floating point operations. | Mayroon itong 29-double precision floating point operations. |

RISC V Verilog Code

Ang instruction memory verilog code para sa RISC ay ipinapakita sa ibaba.

// Verilog code para sa RISC Processor

// Verilog code para sa Instruction Memory

module Instruction_Memory(

input [15:0] pc,

output[15:0] pagtuturo

);

reg [`col – 1:0] memory [`row_i – 1:0];

wire [3 : 0] rom_addr = pc[4 : 1];

inisyal

magsimula

$readmemb(“./test/test.prog”, memorya,0,14);

wakas

magtalaga ng pagtuturo = memory[rom_addr];

endmodule

Verilog code para sa 16-bit na RISC V processor:

module Risc_16_bit(

input clk

);

wire jump,bne,beq,mem_read,mem_write,alu_src,reg_dst,mem_to_reg,reg_write;

wire[1:0] alu_op;

wire [3:0] opcode;

// Daanan ng mga datos

Datapath_Unit DU

(

.clk(clk),

.jump(jump),

.palaka(palaka),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.reg_write(reg_write),

.bne(bne),

.alu_op(alu_op),

.opcode(opcode)

);

// control unit

Control_Unit control

(

.opcode(opcode),

.reg_dst(reg_dst),

.mem_to_reg(mem_to_reg),

.alu_op(alu_op),

.jump(jump),

.bne(bne),

.palaka(palaka),

.mem_read(mem_read),

.mem_write(mem_write),

.alu_src(alu_src),

.reg_write(reg_write)

);

endmodule

Mga Set ng Pagtuturo

Ang mga set ng pagtuturo ng RISC V ay tinatalakay sa ibaba.

Mga Operasyon ng Arithmetic

Ang RISC V arithmetic operations ay nakalista sa ibaba.

| Mnemonic | Uri | Pagtuturo | Paglalarawan |

| ADD rd, rs1, rs2 |

R |

Idagdag | rdß rs1 + rs2 |

| SUB rd, rs1, rs2 |

R |

Ibawas | rdß rs1 – rs2 |

| ADDI rd, rs1, imm12 |

ako |

Idagdag kaagad | rdß rs1 + imm12 |

| SLT rd, rs1, rs2 |

R |

Itakda ang mas mababa sa | rdß rs1 -< rs2 |

| SLTI rd, rs1, imm12 |

ako |

Itakda ang mas mababa sa agarang | rdß rs1 -< imm12 |

| SLTU rd, rs1, rs2 |

R |

Itakda ang mas kaunti kaysa sa hindi nilagdaan | rdß rs1 -< rs2 |

| SLTIU rd, rs1, imm12 |

ako |

Itakda ang mas mababa sa agarang unsigned | rdß rs1 -< imm12 |

| LUI rd, imm20 |

SA |

Mag-load sa itaas kaagad | rdß imm20<<12 |

| AUIP rd,imm20 |

SA |

Magdagdag ng upper immediate sa PC | rdß PC+imm20<<12 |

Mga Lohikal na Operasyon

Ang RISC V logical operations ay nakalista sa ibaba.

| Mnemonic | Uri | Pagtuturo | Paglalarawan |

| AT rd, rs1, rs2 |

R |

AT | rdß rs1 at rs2 |

| O rd, rs1, rs2 |

R |

O | rdß rs1 | rs2 |

| XOR rd, rs1, rs2 |

R |

LIBRE | rdß rs1 ^ rs2 |

| ANDI rd, rs1, imm12 |

ako |

AT kaagad | rdß rs1 at imm2 |

| ORI rd, rs1, imm12 |

ako |

O Kaagad | rdß rs1 | imm12 |

| OXRI rd, rs1, imm12 |

ako |

XOR kaagad | rdß rs1 ^ rs2 |

| SLL rd, rs1, rs2 |

R |

Lumipat pakaliwa lohikal | rdß rs1 << rs2 |

| SRL rd, rs1, rs2 |

R |

Lumipat pakanan lohikal | rdß rs1 >> rs2 |

| RAS rd, rs1, rs2 |

R |

Lumipat pakanan sa aritmetika | rdß rs1 >> rs2 |

| SLLI rd, rs1, shamt |

ako |

Lumipat pakaliwa lohikal kaagad | rdß rs1 << shamt |

| SRLI rd, rs1, shamt |

ako |

Lumipat pakanan lohikal kaagad | rdß rs1 >> shamt |

| SRAI rd, rs1, shamt |

ako |

Agad na lumipat sa kanan ng aritmetika | rdß rs1 >> shamt |

Mga Operasyong Mag-load/Store

Ang RISC V load/store operations ay nakalista sa ibaba.

| Mnemonic | Uri | Pagtuturo | Paglalarawan |

| LD rd, imm12 (rs1) |

ako |

Mag-load ng doubleword | rdß mem [rs1 +imm12] |

| LW rd, imm12 (rs1) |

ako |

Mag-load ng salita | rdß mem [rs1 +imm12] |

| LH rd, imm12 (rs1) |

ako |

Mag-load sa kalahati | rdß mem [rs1 +imm12] |

| LB rd, imm12 (rs1) |

ako |

Mag-load ng byte | rdß mem [rs1 +imm12] |

| LWU rd, imm12 (rs1) |

ako |

Mag-load ng salitang hindi nalagdaan | rdß mem [rs1 +imm12] |

| LHU rd, imm12 (rs1) |

ako |

I-load ang kalahating salita na hindi pinirmahan | rdß mem [rs1 +imm12] |

| LBU rd, imm12 (rs1) |

ako |

I-load ang byte na hindi nalagdaan | rdß mem [rs1 +imm12] |

| SD rs2, imm12 (rs1) |

S |

Mag-imbak ng dobleng salita | rs2 hanggang mem [rs1 +imm12] |

| SW rs2, imm12 (rs1) |

S |

Mag-imbak ng salita | rs2 (31:0) hanggang mem [rs1 +imm12] |

| SH rs2, imm12 (rs1) |

S |

Mag-imbak sa kalahating daan | rs2 (15:0) hanggang mem [rs1 +imm12] |

| SB rs2, imm12 (rs1) |

S |

Mag-imbak ng byte | rs2 (15:0) hanggang mem [rs1 +imm12] |

| SRAI rd, rs1, shamt |

ako |

Agad na lumipat sa kanan ng aritmetika | rs2 (7:0) hanggang mem [rs1 +imm12] |

Mga Operasyon ng Branching

Ang RISC V branching operations ay nakalista sa ibaba.

| Mnemonic | Uri | Pagtuturo | Paglalarawan |

| BEQ rs1, rs2, imm12 |

SB |

Pantay ang sangay | Kung rs1== rs2 PC ß PC+imm12 |

| BNE rs1, rs2, imm12 |

SB |

Hindi pantay ang sangay | Kung rs1!= rs2 PC ß PC+imm12 |

| BGE rs1, rs2, imm12 |

SB |

Sangay na mas malaki sa o katumbas | Kung rs1>= rs2 PC ß PC+imm12 |

| BGEU rs1, rs2, imm12 |

SB |

Sangay na mas malaki sa o katumbas ng hindi nalagdaan | Kung rs1>= rs2 PC ß PC+imm12 |

| BLT rs1, rs2, imm12 |

SB |

Sangay na mas mababa sa | Kung rs1< rs2 PC ß PC+imm12 |

| BLTU rs1, rs2, imm12 |

SB |

Ang branch ay mas mababa sa unsigned | Kung rs1< rs2 PC ß PC+imm12 <<1 |

| JAL rd, imm20 |

UJ |

Tumalon at Mag-link | rdßPC+4 PCß PC+imm20 |

| JALR rd, imm12(rs1) |

ako |

Tumalon at Mag-link ng rehistro | rdßPC+4 PCß rs1+imm12 |

Mga kalamangan

Ang mga pakinabang ng RISC V processor isama ang mga sumusunod.

- Sa pamamagitan ng paggamit ng RISCV, makakatipid tayo ng oras ng pag-develop, pagbuo ng software, pag-verify, atbp.

- Ang processor na ito ay may maraming kalamangan tulad ng pagiging simple, pagiging bukas, modularity, malinis na disenyo ng slate, at extensibility.

- Sinusuportahan ito ng ilang mga compiler ng wika tulad ng GCC (GNU Compiler Collection), isang free-software compiler at sa pamamagitan ng Linux OS .

- Malayang magagamit ito ng mga kumpanya dahil sa walang royalty, walang bayad sa paglilisensya at walang koneksyon.

- Ang RISC-V processor ay hindi kasama ang anumang mga bago o makabagong feature dahil sumusunod lang ito sa mga itinatag na prinsipyo ng RISC.

- Katulad ng ilang iba pang mga ISA, ang detalye ng processor na ito ay tumutukoy lamang sa iba't ibang antas ng set ng pagtuturo. Kaya naglalaman ito ng 32 at 64-bit na mga variant pati na rin ang mga extension upang magbigay ng suporta para sa mga tagubilin sa floating point.

- Ang mga ito ay libre, simple, modular, stable, atbp.

Mga disadvantages

Ang disadvantages ng RISC V processor isama ang mga sumusunod.

- Ang mga kumplikadong tagubilin ay madalas na ginagamit ng mga compiler at programmer.

- Ang o/p ng isang RISC ay maaaring magbago batay sa code kapag ang mga kasunod na tagubilin sa loob ng isang loop ay nakadepende sa naunang tagubilin para sa pagpapatupad.

- Ang mga processor na ito ay kailangang mag-save ng iba't ibang mga tagubilin nang mabilis, na nangangailangan ng isang malaking cache memory set upang tumugon sa pagtuturo sa loob ng isang napapanahong paraan.

- Ang mga kumpletong feature, kakayahan at benepisyo ng RISC ay pangunahing nakadepende sa arkitektura.

Mga aplikasyon

Ang mga aplikasyon ng RISC V processor isama ang mga sumusunod.

- Ginagamit ang RISC-V sa mga naka-embed na system, artificial intelligence, at machine learning.

- Ang mga processor na ito ay ginagamit sa high-performance-based embedded system applications.

- Ang processor na ito ay angkop na gamitin sa ilang partikular na field tulad ng edge computing, AI at storage application.

- Mahalaga ang RISC-V dahil pinapayagan nito ang mas maliliit na tagagawa ng device na magdisenyo ng hardware nang hindi nagbabayad.

- Pinapayagan lamang ng processor na ito ang mga mananaliksik at developer na magdisenyo pati na rin ang pagsasaliksik na may malayang magagamit na ISA o arkitektura ng set ng pagtuturo.

- Ang mga application ng RISC V ay mula sa maliliit na naka-embed na microcontroller hanggang sa mga desktop PC at supercomputer kabilang ang mga vector processor.

Kaya, ito ay isang pangkalahatang-ideya ng isang RISC V Processor – arkitektura, nagtatrabaho sa mga application. Narito ang isang katanungan para sa iyo, ano ang isang CISC processor?