Ang iba't ibang mga uri ng mga Digital system ay itinayo mula sa napakakaunting mga uri ng pangunahing mga pagsasaayos ng network tulad ng AND gate, NAND gate, O gate, atbp ... Ang mga elementong circuit na ito ay ginagamit nang paulit-ulit sa iba't ibang mga topological na kumbinasyon. Bilang karagdagan sa pagsasagawa ng lohika, ang mga digital na system ay dapat ding mag-imbak ng mga binary number. Para sa mga memory cell na ito, na kilala rin bilang TSINELAS' s ay dinisenyo. Upang maisagawa ang ilang mga pag-andar tulad ng pagdaragdag ng binary. Samakatuwid, upang maisagawa ang mga naturang pag-andar, mga kumbinasyon ng mga gate ng lohika at FLIP-FLOPs ay dinisenyo sa loob ng isang solong-chip IC. Ang form ng IC na ito ang praktikal na mga bloke ng pagbuo ng mga Digital system. Ang isa sa mga naturang mga bloke ng gusali na ginamit para sa pagdaragdag ng binary ay ang Carry Look-advance Adder.

Ano ang isang Carry Look-advance Adder?

Ang isang digital computer ay dapat maglaman ng mga circuit na maaaring magsagawa ng mga operasyon sa arithmetic tulad ng pagdaragdag, pagbabawas, pagpaparami, at paghahati. Kabilang sa mga ito, pagdaragdag at pagbabawas ay ang pangunahing mga pagpapatakbo samantalang ang pagpaparami at paghati ay ang paulit-ulit na pagdaragdag at pagbabawas ayon sa pagkakabanggit.

Upang maisagawa ang mga operasyong ito, ipinatupad ang 'Adder circuit' gamit ang pangunahing mga gate ng lohika. Mga adder circuit ay binago bilang Half-adder, Full-adder, Ripple-carry Adder, at Carry Look-advance Adder.

Kabilang sa mga Carry Look-advance Adder na ito ay ang mas mabilis na circuit ng adder. Binabawasan nito ang pagkaantala ng paglaganap, na nangyayari sa panahon ng pagdaragdag, sa pamamagitan ng paggamit ng mas kumplikadong circuitry ng hardware. Ito ay dinisenyo sa pamamagitan ng pagbabago ng ripple-carry Adder circuit tulad ng pagdadala ng lohika ng adder ay binago sa dalawang antas na lohika.

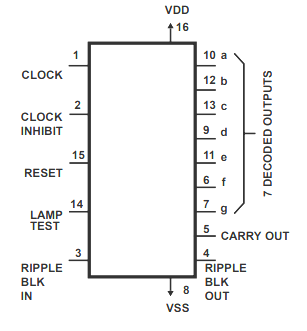

4-Bit Magdala ng Pangharap na Adder

Sa mga parallel na nagdaragdag, ang pagdala ng output ng bawat buong adder ay ibinibigay bilang isang input ng pagdadala sa susunod na mas mataas na order na estado. Samakatuwid, ang mga nagdaragdag na ito ay hindi posible na gumawa ng pagdala at pagsasama ng mga output ng anumang estado maliban kung ang isang input ng pagdadala ay magagamit para sa estado na iyon.

Kaya, para sa computation na maganap, ang circuit ay kailangang maghintay hanggang sa bitbit ang bitbit sa lahat ng mga estado. Ito ay nag-uudyok na magdala ng pagkaantala sa paglaganap sa circuit.

4-bit-Ripple-Carry-Adder

Isaalang-alang ang 4-bit na ripple na nagdadala ng adder circuit sa itaas. Dito maaaring maisagawa ang kabuuan ng S3 sa sandaling maibigay ang mga input na A3 at B3. Ngunit ang pagdala ng C3 ay hindi maaaring kalkulahin hanggang sa ang bitbit C2 ay mailapat samantalang ang C2 ay nakasalalay sa C1. Samakatuwid upang makabuo ng pangwakas na mga resulta ng matatag na estado, ang pagdadala ay dapat magpalaganap sa lahat ng mga estado. Dagdagan nito ang pagkaantala ng pagdala ng pagdala ng circuit.

Ang pagkaantala ng pagpapalaganap ng adder ay kinakalkula bilang 'ang pagkaantala ng paglaganap ng bawat gate na beses sa bilang ng mga yugto sa circuit'. Para sa pagkalkula ng isang malaking bilang ng mga piraso, maraming mga yugto ang kailangang idagdag, na ginagawang mas masahol ang pagkaantala. Samakatuwid, upang malutas ang sitwasyong ito, ipinakilala ang Carry Look-advance Adder.

Upang maunawaan ang paggana ng isang Carry Look-advance Adder, isang 4-bit na Carry Look-advance Adder ay inilarawan sa ibaba.

4-bit-Carry-Look-advance-Adder-Logic-Diagram

Sa adder na ito, ang input ng pagdala sa anumang yugto ng adder ay malaya sa mga bitbit ng bitbit na nabuo sa mga independiyenteng yugto. Dito ang output ng anumang yugto ay nakasalalay lamang sa mga piraso na idinagdag sa mga nakaraang yugto at ang dalang input na ibinigay sa panimulang yugto. Samakatuwid, ang circuit sa anumang yugto ay hindi kailangang maghintay para sa pagbuo ng bitbit na bit mula sa nakaraang yugto at dalhin ang bit ay maaaring masuri sa anumang instant na oras.

Talaan ng Katotohanan ng Magdala ng Maghandang Adder

Para sa pagkuha ng talahanayan ng katotohanan ng adder na ito, dalawang bagong mga termino ang ipinakilala - Dalhin ang bumuo at magdala ng magpalaganap. Dalhin ang bumuo ng Gi = 1 tuwing mayroong dalang dalang Ci + 1 na nabuo. Depende ito sa mga input ng Ai at Bi. Ang Gi ay 1 kung kapwa ang Ai at Bi ay 1. Samakatuwid, ang Gi ay kinakalkula bilang Gi = Ai. Bi.

Ang pagdala ng napalaganap na Pi ay nauugnay sa paglaganap ng pagdala mula Ci hanggang Ci + 1. Kinakalkula ito bilang Pi = Ai ⊕ Bi. Ang talahanayan ng katotohanan ng adder na ito ay maaaring makuha mula sa pagbabago ng talahanayan ng katotohanan ng isang buong adder.

Gamit ang mga katagang Gi at Pi ang Sum Si at Carry Ci + 1 ay ibinibigay tulad ng sa ibaba -

- Si = Pi ⊕ Gi.

- Ci + 1 = Ci.Pi + Gi.

Samakatuwid, ang bitbit na C1, C2, C3, at C4 ay maaaring kalkulahin bilang

- C1 = C0.P0 + G0.

- C2 = C1.P1 + G1 = (C0.P0 + G0) .P1 + G1.

- C3 = C2.P2 + G2 = (C1.P1 + G1) .P2 + G2.

- C4 = C3.P3 + G3 = C0.P0.P1.P2.P3 + P3.P2.P1.G0 + P3.P2.G1 + G2.P3 + G3.

Maaari itong maobserbahan mula sa mga equation na nagdadala ng Ci + 1 ay nakasalalay lamang sa pagdala ng C0, hindi sa mga intermediate na bitbit.

Dala-Hanapin-maaga-Adder-Truth-Table

Diagram ng Circuit

Ang mga equation sa itaas ay ipinatupad gamit ang dalawang antas na mga kombinasyon ng kombinasyon kasama ang AT, O mga pintuang-bayan, kung saan ipinapalagay na may maraming mga input ang mga pintuan.

Carry-Output-Generation-Circuit-of-Carry-Look-advance-Adder

Ang Carry Look-advance Adder circuit papunta sa 4-bit ay ibinibigay sa ibaba.

4-bit-Carry-Look-advance-Adder-Circuit-Diagram

Ang 8-bit at 16-bit na Carry Look-advance Adder circuit ay maaaring idisenyo sa pamamagitan ng pag-cascading ng 4-bit adder circuit na may dalang lohika.

Mga kalamangan ng Carry Look-advance Adder

Sa adder na ito, ang pagkaantala ng pagpapalaganap ay nabawasan. Ang output ng pagdala sa anumang yugto ay nakasalalay lamang sa paunang bitbit ng panimulang yugto. Gamit ang adder na ito posible na kalkulahin ang mga intermediate na resulta. Ang adder na ito ay ang pinakamabilis na adder na ginamit para sa pagkalkula.

Mga Aplikasyon

Ang mga high-speed Carry Look-forward Adder ay ginagamit bilang ipinatupad bilang IC's. Samakatuwid, madaling i-embed ang adder sa mga circuit. Sa pamamagitan ng pagsasama ng dalawa o higit pang mga kalkulasyon ng mga nagdaragdag ng mas mataas na pag-andar ng boolean ay madaling magawa. Dito ang pagtaas sa bilang ng mga pintuang katamtaman din kapag ginamit para sa mas mataas na mga piraso.

Para sa Adder na ito mayroong isang tradeoff sa pagitan ng lugar at bilis. Kapag ginamit para sa mas mataas na mga kalkulasyon ng bit, nagbibigay ito ng mataas na bilis ngunit ang pagiging kumplikado ng circuit ay nadagdagan din sa gayon pagtaas ng lugar na sinakop ng circuit. Ang adder na ito ay karaniwang ipinatutupad bilang 4-bit modules na isinasabay na kaskad kapag ginamit para sa mas mataas na mga kalkulasyon. Ang adder na ito ay mas mahal kung ihahambing sa ibang mga nagdaragdag.

Para sa pagkalkula ng boolean sa mga computer, regular na ginagamit ang mga adder. Si Charles Babbage ay nagpatupad ng isang mekanismo para sa pag-asa sa bitbit ng bitbit sa mga computer, upang mabawasan ang pagkaantala na dulot ng mga nagdadala ng ripple . Habang nagdidisenyo ng isang sistema, ang bilis ng pagkalkula ay ang pinakamataas na kadahilanan ng pagpapasya para sa isang taga-disenyo. Noong 1957, pinatawad ni Gerald B. Rosenberger ang modernong Binary Carry Look-advance Adder. Batay sa pagsusuri ng pagkaantala at pag-simulate ng gate, isinasagawa ang mga eksperimento upang mabago ang circuit ng adder na ito upang mas mabilis itong gawin. Para sa isang n-bit na tumitingin na adder, ano ang pagkaantala ng paglaganap, kapag binigyan ng pagkaantala ng bawat gate ay 20?

Credit sa Imahe