Mayroong isang panahon, kung saan ang mga computer ay tulad ng malaking sukat sa laki upang mai-install ang mga ito, madali kailangan ng puwang sa silid. Ngunit ngayon sila ay umunlad na sa gayon ay madali nating madadala ang mga ito bilang mga notebook. Ang makabagong ideya na ginawang posible ito ay ang konsepto ng Integrated Circuits. Sa Pinagsamang Circuits , isang malaking bilang ng mga aktibo at mga elemento ng passive kasama ang kanilang mga pagkakaugnay ay binuo sa isang maliit na silicon wafer na karaniwang 50 hanggang 50 mils sa cross section. Ang mga pangunahing proseso na sinusundan para sa paggawa ng naturang mga circuit ay kasama ang paglago ng epitaxial, masked impurity diffusion, paglago ng oksido, at pag-ukit ng oxide, gamit ang photolithography para sa paggawa ng pattern.

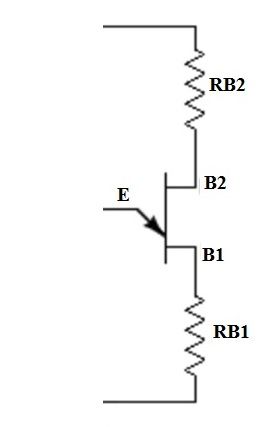

Ang mga sangkap sa wafer ay may kasamang mga resistors, transistor, diode, capacitor atbp ... Ang pinaka-kumplikadong sangkap na gagawin sa paglipas ng IC ay mga transistor. Ang mga transistor ay may iba't ibang uri tulad ng CMOS, BJT, FET. Pinipili namin ang uri ng teknolohiyang transistor na ipapatupad sa isang IC batay sa mga kinakailangan. Sa artikulong ito ipaalam sa amin pamilyar sa konsepto ng Paggawa ng CMOS (o) katha ng mga transistors bilang CMOS.

Paggawa ng CMOS

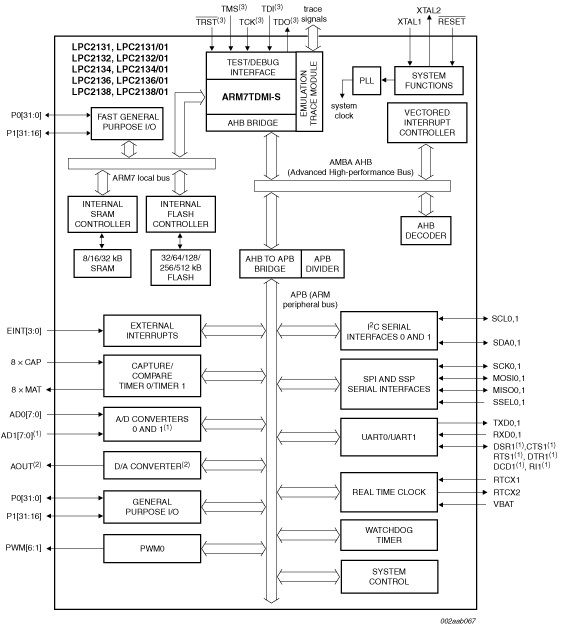

Para sa mas kaunting kinakailangan sa pagwawaldas ng kuryente Teknolohiya ng CMOS ay ginagamit para sa pagpapatupad ng transistors. Kung nangangailangan kami ng isang mas mabilis na circuit pagkatapos ay ipatupad ang mga transistors Gamit ng IC BJT . Paggawa ng Mga transistor ng CMOS tulad ng IC's ay maaaring gawin sa tatlong magkakaibang pamamaraan.

Ang teknolohiyang N-well / P-well, kung saan ang n-type diffusion ay ginagawa sa isang p-type substrate o p-type diffusion ay tapos na sa n-type substrate ayon sa pagkakabanggit.

Ang Teknolohiya ng kambal na rin , saan NMOS at PMOS transistor ay binuo sa ibabaw ng manipis na tinapay sa pamamagitan ng sabay-sabay na pagsasabog sa isang epitaxial na base ng paglago, sa halip na isang substrate.

Ang proseso ng silicon On Insulator, kung saan sa halip na gumamit ng silikon bilang substrate isang materyal na insulator ay ginagamit upang mapabuti ang bilis at pagkabitin ng latch-up.

N- maayos / P- mahusay Teknolohiya

Ang CMOS ay maaaring makuha sa pamamagitan ng pagsasama ng pareho Mga transistor ng NMOS at PMOS higit sa parehong silicon wafer. Sa teknolohiyang N – balon ang isang n-uri na balon ay nagkakalat sa isang p-uri na substrate samantalang sa P- mabuti ito ay bisyo.

Mga Hakbang sa Paggawa ng CMOS

Ang Proseso ng paggawa ng CMOS dumaloy ay isinasagawa gamit ang dalawampu pangunahing mga hakbang sa katha habang gawa gamit ang teknolohiyang N- maayos / P-balon.

Paggawa ng CMOS gamit ang N ng maayos

Hakbang 1: Pumili muna kami ng isang substrate bilang isang batayan para sa katha. Para sa N- mabuti, isang p-uri ng silicon substrate ang napili.

Substrate

Hakbang 2 - oksihenasyon: Ang pumipili na pagsasabog ng mga n-type na impurities ay nagagawa gamit ang SiO2 bilang isang hadlang na nagpoprotekta sa mga bahagi ng manipis na tinapay laban sa kontaminasyon ng substrate. SiOdalawaay inilatag sa pamamagitan ng proseso ng oksihenasyon tapos na paglalantad ng substrate sa de-kalidad na oxygen at hydrogen sa isang silid ng oksihenasyon na humigit-kumulang na 10000c

Oksihenasyon

Hakbang 3 - Lumalagong Photoresist: Sa yugtong ito upang pahintulutan ang pumipili ng pag-ukit, ang layer ng SiO2 ay napailalim sa proseso ng photolithography. Sa prosesong ito, ang manipis na tinapay ay pinahiran ng isang pare-parehong pelikula ng isang photosensitive emulsyon.

Lumalagong Photoresist

Hakbang 4 - Masking: Ang hakbang na ito ay ang pagpapatuloy ng proseso ng photolithography. Sa hakbang na ito, ang isang nais na pattern ng pagiging bukas ay ginawa gamit ang isang stencil. Ang stencil na ito ay ginagamit bilang isang maskara sa photoresist. Ang substrate ay nakalantad na ngayon sa Mga sinag ng UV ang photoresist na naroroon sa ilalim ng mga nakalantad na mga rehiyon ng mask ay nakapag-polymerize.

Masking ng Photoresist

Hakbang 5 - Pag-aalis ng Unexposed Photoresist: Ang maskara ay tinanggal at ang hindi nakalantad na rehiyon ng photoresist ay natunaw sa pamamagitan ng pagbuo ng wafer gamit ang isang kemikal tulad ng Trichlorethylene.

Pag-aalis ng Photoresist

Hakbang 6 - Pagkulit: Ang manipis na tinapay ay nahuhulog sa isang solusyon sa pag-ukit ng hydrofluoric acid, na tinatanggal ang oksido mula sa mga lugar kung saan naisasabog ang mga dopant.

Pagkulit ng SiO2

Hakbang 7 - Pag-aalis ng Buong Photoresist Layer: Sa panahon ng proseso ng pag-ukit , ang mga bahagi ng SiO2 na protektado ng photoresist layer ay hindi apektado. Ang maskara ng photoresist ngayon ay hinubaran ng isang kemikal na may kakayahang makabayad ng utang (mainit na H2SO4).

Pag-aalis ng Photoresist Layer

Hakbang 8 - Pagbuo ng N-well: Ang mga n-type na impurities ay nagkakalat sa p-type substrate sa pamamagitan ng nakalantad na rehiyon kung kaya bumubuo ng isang N- well.

Pagbuo ng N-well

Hakbang 9 - Pag-aalis ng SiO2: Ang layer ng SiO2 ay tinanggal ngayon sa pamamagitan ng paggamit ng hydrofluoric acid.

Pag-aalis ng SiO2

Hakbang 10 - Paglalagay ng Polysilicon: Ang maling pagkakahanay ng gate ng a CMOS transistor ay hahantong sa hindi kanais-nais na capacitance na maaaring makapinsala sa circuit. Kaya upang maiwasan ang 'Sariling proseso ng gate na nakahanay' na ito ay ginustong kung saan nabuo ang mga rehiyon ng gate bago ang pagbuo ng mapagkukunan at alisan ng tubig gamit ang ion implantation.

Paglalagay ng Polysilicon

Ginagamit ang Polysilicon para sa pagbuo ng gate sapagkat matatagalan nito ang mataas na temperatura na higit sa 80000c kapag ang isang manipis na tinapay ay napailalim sa mga pamamaraan ng pagsusubo para sa pagbuo ng mapagkukunan at alisan ng tubig. Ang Polysilicon ay idineposito sa pamamagitan ng paggamit Proseso ng Deposisyon ng Kemikal sa isang manipis na layer ng gate oxide. Ang manipis na gate oxide na ito sa ilalim ng layer ng Polysilicon ay pumipigil sa karagdagang pag-doping sa ilalim ng rehiyon ng gate.

Hakbang 11 - Pagbuo ng Rehiyon ng Gate: Maliban sa dalawang rehiyon na kinakailangan para sa pagbuo ng gate para sa Mga transistor ng NMOS at PMOS ang natitirang bahagi ng Polysilicon ay tinanggal.

Pagbuo ng Rehiyon ng Gate

Hakbang 12 - Proseso ng oksihenasyon: Ang isang layer ng oksihenasyon ay idineposito sa ibabaw ng manipis na tinapay na nagsisilbing isang kalasag para sa karagdagang pagsasabog at proseso ng metallization .

Proseso ng oksihenasyon

Hakbang 13 - Masking at Diffusion: Para sa paggawa ng mga rehiyon para sa pagsasabog ng mga n-type na impurities gamit ang proseso ng masking maliit na mga puwang ay ginawa.

Masking

Ang paggamit ng proseso ng pagsasabog ng tatlong n + rehiyon ay binuo para sa pagbuo ng mga terminal ng NMOS.

N-pagsasabog

Hakbang 14 - Pag-aalis ng Oxide: Ang layer ng oksido ay hinubaran.

Pag-aalis ng Oxide

Hakbang 15 - P-type na Diffusion: Katulad ng n-type diffusion para sa pagbuo ng mga terminal ng PMOS p-type diffusion ay isinasagawa.

P-Type Diffusion

Hakbang 16 - Pagtula ng Makapal na Field oxide: Bago ang pagbuo ng mga metal terminal ay inilalagay ang isang makapal na field oxide upang makabuo ng isang proteksiyon layer para sa mga rehiyon ng manipis na tinapay kung saan walang kinakailangang mga terminal.

Makapal na Field oxide Layer

Hakbang 17 - Metallization: Ang hakbang na ito ay ginagamit para sa pagbuo ng mga metal terminal na maaaring magbigay ng mga pagkakaugnay. Ang aluminyo ay kumakalat sa buong manipis na tinapay.

Metallisasyon

Hakbang 18 - Pag-aalis ng Labis na Metal: Ang labis na metal ay tinanggal mula sa wafer.

Hakbang 19 - Pagbuo ng mga Terminal: Sa mga puwang na nabuo pagkatapos ng pagtanggal ng labis na mga terminal ng metal ay nabuo para sa mga pagkakaugnay.

Pagbuo ng mga Terminal

Hakbang 20 - Pagtatalaga ng Mga Pangalan ng Terminal: Ang mga pangalan ay nakatalaga sa mga terminal ng Mga transistor ng NMOS at PMOS .

Pagtatalaga ng mga pangalan ng Terminal

Paggawa ng CMOS gamit ang P well Technology

Ang proseso ng p-balon ay katulad ng proseso ng maayos na N maliban dito na ginagamit ang uri ng n-uri na substrate at isinasagawa ang mga diffusion na uri ng p. Para sa pagiging simple dati, ginustong proseso ng N na rin.

Twin Tube Fabrication ng CMOS

Ang paggamit ng proseso ng Twin-tube ay maaaring makontrol ng isang tao ang mga aparato ng P at N-type. Iba't ibang mga hakbang na kasangkot sa katha ng CMOS gamit ang paraan ng Twin-tube ay ang mga sumusunod

- Ang isang gaanong naka-doped n o p-type na substrate ay kinuha at ginagamit ang epitaxial layer. Pinoprotektahan ng Epitaxial layer ang problema sa pag-alma sa maliit na tilad.

- Ang mataas na dalisay na mga layer ng silikon na may sinusukat na kapal at eksaktong konsentrasyon ng dopant ay lumago.

- Pagbuo ng mga tubo para sa P at N na rin.

- Manipis na pagtatayo ng oksido para sa proteksyon mula sa kontaminasyon sa panahon ng mga proseso ng pagsasabog.

- Ang mapagkukunan at alisan ng tubig ay nabuo gamit ang mga pamamaraan ng pagtatanim ng ion.

- Ginagawa ang mga pagputol para sa paggawa ng mga bahagi para sa mga contact sa metal.

- Ginagawa ang metallization para sa pagguhit ng mga contact sa metal

Layout ng CMOS IC

Ang itaas na pagtingin ng sa CMOS katha at layout ay ibinigay. Dito iba't ibang mga contact sa metal at N well diffusions ay maaaring matingnan nang malinaw.

Layout ng CMOS IC

Kaya, ito ay tungkol sa lahat Mga diskarte sa paggawa ng CMOS . Isaalang-alang natin ang isang 1-in-square wafer na nahahati sa 400 chips ng ibabaw na lugar na 50 mil ng 50 mils. Tumatagal ng isang lugar na 50 mil2 upang makagawa ng isang transistor. Samakatuwid ang bawat IC ay naglalaman ng 2 transistors sa gayon mayroong 2 x 400 = 800 transistors na itinayo sa bawat manipis na tinapay. Kung 10 mga manipis na tinapay ang naproseso sa bawat batch kung gayon ang 8000 transistors ay maaaring gawa nang sabay-sabay. Ano ang iba`t ibang mga bahagi na napansin mo sa isang IC?