Ipinapaliwanag ng artikulong ito ang henerasyon ng modulate ng lapad ng pulso signal na may variable duty cycle sa FPGA gamit ang VHDL. Ang PWM ay may isang nakapirming dalas at isang variable boltahe. Tinalakay din ng artikulong ito ang Digital Clock Manager para sa pagbawas ng dalas ng orasan sa pamamagitan ng pagbawas ng hiwi ng signal ng orasan. Ginagamit ang isang nakapirming dalas upang makagawa ng input data na gumagawa ng mga signal ng PWM gamit ang isang kumpare. Ang mga elektronikong kumpanya ay nagdidisenyo ng hardware na nakatuon sa kanilang mga produkto sa kanilang mga pamantayan at protokol na ginagawang hamon para sa mga end user na mai-configure muli ang hardware ayon sa kanilang mga pangangailangan. Ang kinakailangang ito para sa hardware ay humantong sa paglago ng isang bagong segment ng customer-configure programmable na integrated integrated circuit na tinatawag na FPGAs .

Pulse Width Modulation (PWM)

Ang modulasyon ng lapad ng pulso ay malawakang ginagamit sa mga aplikasyon ng komunikasyon at mga control system . Ang pagbuo ng lapad ng pulso ay maaaring mabuo gamit ang iba't ibang mga diskarte sa mga control system. Dito, sa artikulong ito, ang PWM ay nabuo gamit ang Hardware Desk Wika (VHDL) at ipinatupad sa FPGA. Ang pagpapatupad ng PWM sa FPGA ay maaaring maproseso ang data nang mas mabilis at ang arkitektura ng controller ay maaaring ma-optimize para sa puwang o bilis.

Ang PWM ay isang pamamaraan upang magbigay ng lohika na '0' at lohika na '1' para sa isang kontroladong tagal ng panahon. Ito ay isang mapagkukunan ng signal na nagsasangkot ng pagbabago ng kanyang cycle ng tungkulin upang makontrol ang dami ng kuryenteng ipinadala sa pagkarga. Sa PWM, ang tagal ng panahon ng parisukat na alon ay pinananatiling pare-pareho at ang oras kung saan mananatili ang signal ay TAAS ay iba-iba.

Bumubuo ang PWM ng mga pulso sa output nito sa isang paraan na ang average na halaga ng HIGHs at LOWs ay proporsyonal sa input ng PWM. Ang cycle ng tungkulin ng signal ay maaaring iba-iba. Ang isang signal ng PWM ay isang pare-pareho na square square na alon na may iba't ibang cycle ng tungkulin. Iyon ay, ang dalas ng signal ng PWM ay pare-pareho, ngunit ang tagal ng panahon ng signal ay mananatiling mataas at nag-iiba tulad ng ipinakita.

PWM Signal

VHDL

Ang VHDL ay isang wika, ginamit upang ilarawan ang pag-uugali ng mga disenyo ng digital circuit . Ang VHDL ay ginagamit ng mga industriya at akademiko para sa hangarin ng simulate ng mga digital circuit. Ang disenyo nito ay maaaring gayahin at isalin sa form na angkop para sa pagpapatupad sa hardware.

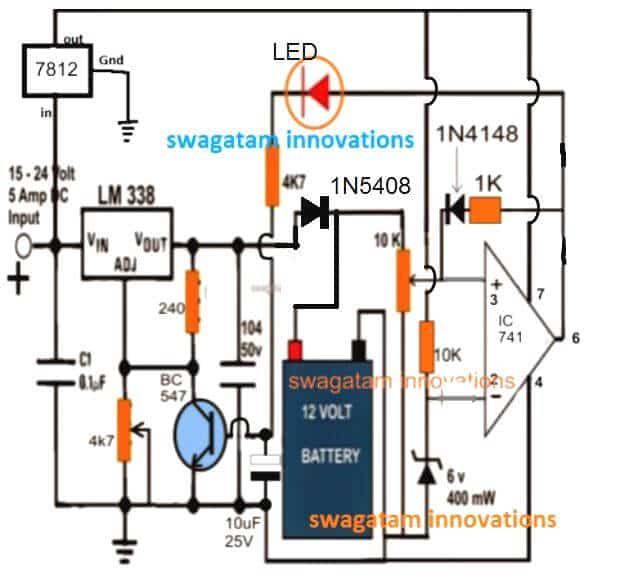

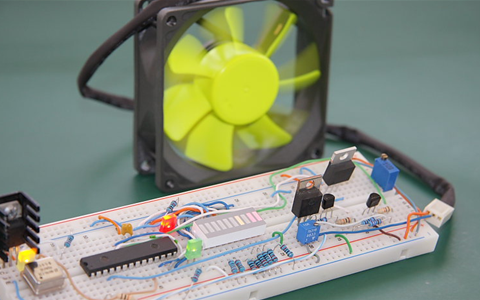

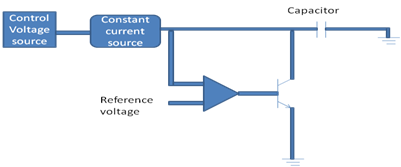

Arkitektura ng PWM

Upang makagawa ng data ng pag-input upang makabuo ng PWM gamit ang isang high-speed N-bit na libreng counter na tumatakbo, na ang output ay inihambing sa rehistro na output at mga tindahan na nais na input duty cycle sa tulong ng kumpare. Ang kumpare ang output ay nakatakda sa 1 kapag pareho ang mga halagang ito. Ang output ng kumpara ay ginagamit upang maitakda ang RS aldaba. Ang overflow signal mula sa counter ay ginagamit upang i-reset ang RS latch. Ang output ng trangka ng RS nagbibigay ng nais na output ng PWM. Ginagamit din ang overflow signal na ito upang mag-load ng bagong N-bit na cycle ng tungkulin sa Rehistro. Ang PWM ay may isang nakapirming dalas at isang variable boltahe. Ang halaga ng boltahe na ito ay nagbabago mula 0V hanggang 5 V.

Signal ng PWM na may variable cycle ng tungkulin

Ang pangunahing PWM ay bumubuo ng mga signal, na nagbibigay ng output ng PWM, ay nangangailangan ng isang kumpara na naghahambing sa pagitan ng dalawang mga halaga. Ang unang halaga ay kumakatawan sa parisukat na signal na nabuo ng N bit counter at ang pangalawang halaga ay kumakatawan sa square signal na naglalaman ng impormasyon tungkol sa duty cycle. Bumubuo ang counter ng signal ng pag-load tuwing mayroong isang overflow. Kapag naging aktibo ang signal ng pag-load, naglo-load ang rehistro ng bagong halaga ng cycle ng tungkulin. Ginagamit ang signal ng pag-load upang i-reset din ang aldaba. Ang output ngatch ay isang senyas ng PWM. Nag-iiba ito sa pagbabago ng halaga ng cycle ng tungkulin.

Ano ang FPGA?

Ang FPGA ay Field Programmable Gate Array. Ito ay isang uri ng aparato na malawakang ginagamit sa mga elektronikong circuit. Ang mga FPGA ay mga aparato ng semiconductor na naglalaman ng maaaring mai-program na mga bloke ng lohika at mga koneksyon ng circuit. Maaari itong mai-program o i-program muli sa kinakailangang pag-andar pagkatapos ng paggawa.

FPGA

Mga pangunahing kaalaman sa FPGA

Kapag ang isang circuit board ay panindang at kung naglalaman ito ng isang FPGA bilang isang bahagi nito. Ito ay nai-program sa panahon ng proseso ng pagmamanupaktura at karagdagang maaaring ma-program muli sa ibang pagkakataon upang lumikha ng isang pag-update o gumawa ng mga kinakailangang pagbabago. Ang tampok na ito ng FPGA ay ginagawang natatangi mula sa ASIC. Ang Application Tukoy na Mga Integrated Circuits (ASIC) ay pasadyang ginawa para sa tiyak na gawain sa disenyo. Sa nakaraan FPGAs ay ginagamit upang bumuo ng mababang bilis, pagiging kumplikado at disenyo ng lakas ng tunog, ngunit ngayon FPGA ay madaling itulak ang pagganap ng hadlang hanggang sa 500MHz.

Sa mga microcontroller, ang chip ay idinisenyo para sa isang customer at kailangan nilang isulat ang software at i-compile ito sa hex file upang mai-load sa microcontroller. Ang software na ito ay maaaring madaling mapalitan dahil ito ay naka-imbak sa flash memory. Sa FPGAs, walang processor upang patakbuhin ang software at kami ang nagdidisenyo ng circuit. Maaari naming mai-configure ang isang FPGA na kasing simple ng isang AND gate o isang komplikadong bilang isang multi-core na processor. Upang lumikha ng isang disenyo nagsusulat kami ng Wika ng Paglalarawan sa Hardware (HDL), na may dalawang uri - Verilog at VHDL. Pagkatapos ang HDL ay na-synthesize sa isang maliit na file gamit ang isang BITGEN upang i-configure ang FPGA. Ang FPGA ay nag-iimbak ng pagsasaayos sa RAM, iyon ang pagsasaayos ay nawala kapag walang pagkakakonekta ng kuryente. Samakatuwid, dapat na mai-configure ang mga ito sa tuwing ibibigay ang lakas.

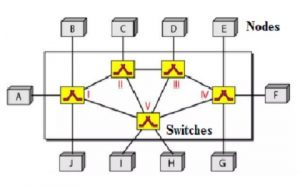

Arkitektura ng FPGA

Ang mga FPGA ay prefabricated na mga chip ng silikon na maaaring mai-program nang kuryente upang magpatupad ng mga digital na disenyo. Ang unang static memory based FPGA na tinatawag na SRAM ay ginagamit para sa pag-configure ng parehong lohika at pagkakaugnay gamit ang isang stream ng mga config bit. Ang modernong EPGA ngayon ay naglalaman ng humigit-kumulang na 3,30,000 mga bloke ng lohika at humigit-kumulang na 1,100 na mga input at output.

Arkitektura ng FPGA

Ang arkitektura ng FPGA ay binubuo ng tatlong pangunahing mga bahagi

- Programmable Logic Blocks, na nagpapatupad ng mga pagpapaandar sa lohika

- Programmable Routing (magkakaugnay), na nagpapatupad ng mga pagpapaandar

- I / O mga bloke, na ginagamit upang makagawa ng mga koneksyon na off-chip

Mga aplikasyon ng signal ng PWM

Ang mga signal ng PWM ay malawakang ginagamit para sa mga aplikasyon ng kontrol. Tulad ng pagkontrol sa mga DC motor, control valve, pump, hydraulics, atbp Narito ang ilang mga application ng mga signal ng PWM.

- Mga sistema ng pag-init na may mabagal na beses 10 hanggang 100Hz o mas mataas.

- DC electric motors 5 hanggang 10KHz

- Mga power supply o audio amplifier na 20 hanggang 200 KHz.

Ang artikulong ito ay tungkol sa pagbuo ng mga signal ng PWM na may variable na cycle ng tungkulin gamit ang FPGA. Bukod dito, para sa anumang tulong sa mga elektronikong proyekto o pagdududa tungkol sa artikulong ito, maaari kang makipag-ugnay sa amin sa pamamagitan ng pagbibigay ng puna sa seksyon ng komento na ibinigay sa ibaba.