Ang mga kombinasyon ng kombinasyon huwag gumamit ng anumang uri ng memorya. Samakatuwid, ang mas maagang posisyon ng pag-input ay hindi nagsasama ng anumang resulta sa kasalukuyang sitwasyon ng circuit. Bagaman, ang sunud-sunod na circuit ay may kasamang memorya dahil dito ang output ay nakasalalay sa pag-input na nangangahulugang ang output ay maaaring magbago batay sa pag-input. Ang pagtatrabaho ng mga circuit na ito ay maaaring gawin sa pamamagitan ng paggamit ng nakaraang circuit input, CLK, memorya, at output. Tinalakay sa artikulong ito ang isang pangkalahatang ideya ng master-slave flip flop. Ngunit bago malaman ang tungkol sa flip-flop na ito, kailangang malaman ang tungkol sa mga pangunahing kaalaman sa tsinelas tulad ng SR flip flop at JK flip flop.

Ano ang isang Master-Slave Flip Flop?

Talaga, ang ganitong uri ng flip flop ay maaaring idisenyo na may dalawang JK FF sa pamamagitan ng pagkonekta sa serye. Isa sa mga FF na ito, ang isang FF ay gumagana bilang master pati na rin ang iba pang FF ay gumagana bilang isang alipin. Ang koneksyon ng mga FF na ito ay maaaring gawin tulad nito, ang output ng master FF ay maaaring konektado sa mga input ng alipin FF. Dito ang mga output ng alipin FF ay maaaring konektado sa mga input ng master FF.

Sa ganitong uri ng FF, isang inverter ginagamit din bilang karagdagan sa dalawang FF. Ang koneksyon ng inverter ay maaaring gawin sa isang paraan na kung saan ang baligtad na CLK pulso ay maaaring konektado sa alipin FF. Sa ibang mga termino, kung ang CLK pulso ay 0 para sa isang master FF, kung gayon ang CLK pulse ay magiging 1 para sa isang alipin FF. Katulad nito, kapag ang CLK pulse ay 1 para sa master FF, kung gayon ang CLK pulse ay magiging 0 para sa alipin FF.

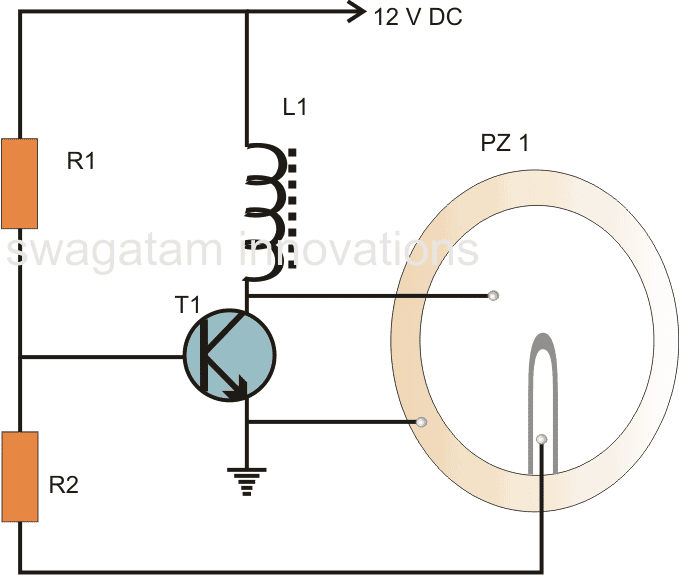

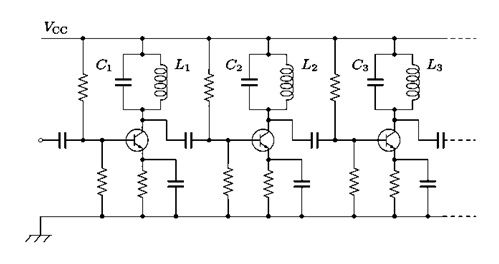

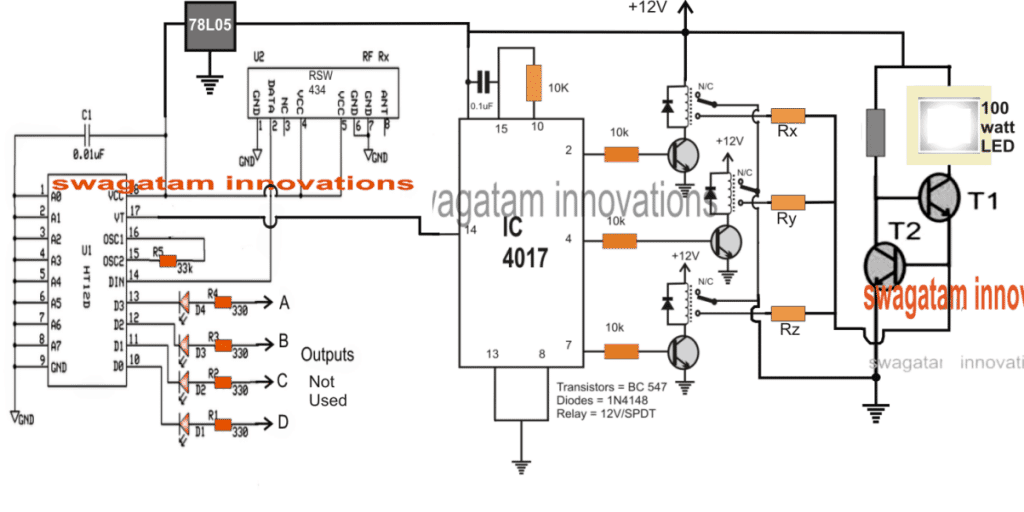

master-slave-flip-flop-circuit

Nagtatrabaho ang Master-Slave FF

Tuwing ang CLK pulso ay napunta sa mataas na nangangahulugang 1, pagkatapos ay maaaring paghiwalayin ng alipin ang mga input tulad ng J & K na maaaring baguhin ang kondisyon ng system.

Ang alipin FF ay maaaring maging hiwalay hanggang sa ang CLK pulso ay bumaba na nangangahulugang 0. Kailanman ang CLK pulso ay bumalik sa mababang estado, pagkatapos ang data ay maaaring mailipat mula sa master FF sa alipin FF at sa wakas, ang o / p maaaring makuha.

Sa una, ang master FF ay mai-trigger sa isang positibong antas samantalang ang alipin FF ay ma-trigger sa isang negatibong antas. Dahil sa kadahilanang ito, ang master FF muna ang tumutugon.

Kung J = 0 & K = 1, pagkatapos ang output ng master FF 'Q' ay pupunta sa input K ng alipin FF & pinipilit ng CLK ang alipin FF na RST (i-reset), samakatuwid ang kopya FF ay kumopya sa panginoon FF.

Kung J = 1 & K = 0, kung gayon ang master FF 'Q' ay pupunta sa input J ng alipin FF & ang negatibong paglipat ng CLK ay nagtatakda sa alipin FF, at kinopya ang panginoon.

Kung J = 1 & K = 1, pagkatapos ay nagpapalipat-lipat ito sa positibong paglipat ng CLK at samakatuwid ang toggle ay nagpapalipat-lipat sa negatibong paglipat ng CLK.

Kung ang parehong J & K ay 0, kung gayon ang FF ay maaaring ma-immobilize at ang Q ay mananatiling hindi masiyahan.

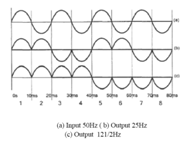

Timing Diagram

- Kapag pareho ang CLK pulse & o / p ng master ay mataas, pagkatapos ito ay mananatiling mataas hanggang ang CLK ay mababa dahil sa estado ay naka-imbak.

- Sa kasalukuyan, ang o / p ng master ay nagiging mababa habang ang CLK pulso ay naging mataas na minsan pa at nananatiling mababa hanggang sa ang CLK ay maging mataas na minsan pa.

- Samakatuwid ang toggling ay nagaganap para sa isang cycle ng CLK.

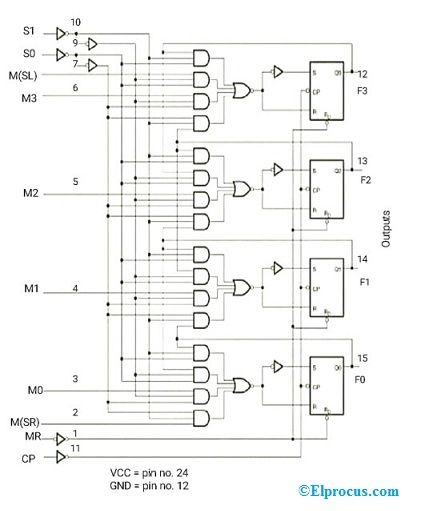

tiyempo-diagram-ng-isang-master-alipin-FF

- Sa tuwing ang CLK pulso ay 1, ang master ay itinakda gayunpaman hindi ang alipin, samakatuwid, ang alipin o / p ay mananatiling '0' hanggang ang CLK ay mananatiling 1.

- Kapag ang CLK ay mababa, pagkatapos ang alipin ay naging pagpapatakbo at mananatiling '1' hanggang sa ang CLK ay muling maging '0'.

- Ang pag-toggg ay nagaganap sa buong buong pamamaraan habang ang o / p ay binabago ng isang oras sa loob ng isang cycle.

- Ginagawa nitong flip flop ito bilang isang kasabay na patakaran ng pamahalaan dahil nagpapasa lamang ito ng data sa tiyempo ng signal ng CLK.

Kaya, ito ay tungkol sa Master-Slave Tsinelas . Mula sa nabanggit na impormasyon, sa wakas, maaari nating tapusin na ang FF na ito ay maaaring mabuo kasama ng dalawang FF na iyon ay ang panginoon at alipin. Kapag ang isang FF ay kumikilos tulad ng master circuit, ito ay aktibo sa itaas ng nangungunang gilid ng CLK pulso. Katulad nito, kapag ang isa pang FF ay kumikilos tulad ng circuit ng alipin, pagkatapos ay aktibo ito sa pagbagsak ng gilid ng CLK pulso.