Ang hanay ng pagtuturo o pagtuturo ng arkitektura ay ang istraktura ng computer na nagbibigay ng mga utos sa computer upang gabayan ang computer para sa pagproseso ng pagmamanipula ng data. Ang hanay ng pagtuturo ay binubuo ng mga tagubilin, addressing mode, katutubong uri ng data, pagrehistro, makagambala, paghawak ng pagbubukod at arkitektura ng memorya. Ang tagubilin ng pagtuturo ay maaaring gayahin sa software sa pamamagitan ng paggamit ng isang interpreter o built sa hardware ng processor. Ang Tagubilin sa Itakda ng Tagubilin ay maaaring isaalang-alang bilang isang hangganan sa pagitan ng software at hardware. Pag-uuri ng mga microcontroller at ang mga microprocessor ay maaaring gawin batay sa arkitektura ng set ng pagtuturo ng RISC at CISC.

Pagtuturo ng hanay ng Processor

Tinutukoy ng hanay ng tagubilin ang pag-andar ng processor kasama ang mga pagpapatakbo na suportado ng processor, mga mekanismo ng imbakan ng processor, at ang paraan ng pag-iipon ng mga programa sa processor.

Ano ang RISC at CISC?

Ang RISC at CISC maaaring mapalawak tulad ng sumusunod:

Kinakatawan ng RISC ang Computer na Nabawasan ng Pagtuturo at

Kinakatawan ng CISC ang Computer na Itinuturo ang Komplikadong Itakda.

Arkitektura ng RISC (Reduced Instruction Set Computer)

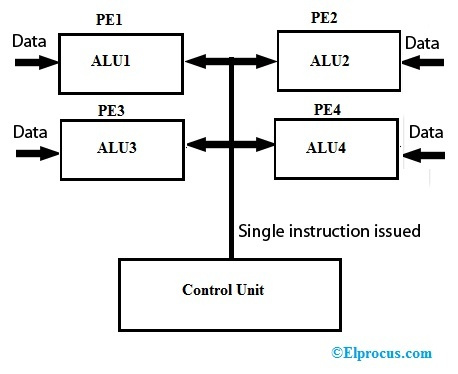

Arkitektura ng RISC

Ang arkitektura ng microcontroller na gumagamit ng maliit at lubos na na-optimize na hanay ng mga tagubilin ay tinatawag na Reduced Instruction Set Computer o simpleng tinawag bilang RISC. Tinatawag din itong arkitektura ng LOAD / STORE.

Sa huling bahagi ng 1970s at unang bahagi ng 1980s, ang mga proyekto ng RISC ay pangunahing binuo mula sa Stanford, UC-Berkley at IBM. Ang koponan ng pagsasaliksik ng John Coke ng IBM ay gumawa ng RISC sa pamamagitan ng pagbawas ng bilang ng mga tagubiling kinakailangan para sa pagpoproseso ng mga pagkalkula nang mas mabilis kaysa sa CISC. Ang arkitektura ng RISC ay mas mabilis at ang mga chips na kinakailangan para sa paggawa ng arkitektura ng RISC ay mas mura rin kumpara sa arkitektura ng CISC.

Mga Karaniwang Tampok ng RISC Architecture

- Ang diskarteng pipelining ng RISC, ay nagpapatupad ng maraming bahagi o yugto ng mga tagubilin nang sabay-sabay na ang bawat pagtuturo sa CPU ay na-optimize. Samakatuwid, ang mga nagpoproseso ng RISC ay mayroong Clock bawat Pagtuturo ng isang pag-ikot, at ito ay tinawag bilang One Cycle Execution.

- Ina-optimize nito ang paggamit ng rehistro na may higit na bilang ng mga rehistro sa RISC at higit na bilang ng mga pakikipag-ugnayan sa loob ng memorya ay maaaring mapigilan.

- Ang mga simpleng mode sa pag-address, kahit na ang kumplikadong pagtugon ay maaaring gawin sa pamamagitan ng paggamit ng arithmetic AT / O lohikal na pagpapatakbo .

- Pinapasimple nito ang disenyo ng tagatala sa pamamagitan ng paggamit ng magkatulad na pangkalahatang mga rehistro ng layunin na nagpapahintulot sa anumang rehistro na magamit sa anumang konteksto.

- Para sa mahusay na paggamit ng mga rehistro at pag-optimize ng paggamit ng pipelining, kinakailangan ang nabawasan na hanay ng pagtuturo.

- Ang bilang ng mga piraso na ginamit para sa opcode ay nabawasan.

- Sa pangkalahatan mayroong 32 o higit pang mga rehistro sa RISC.

Mga kalamangan ng arkitektura ng RISC processor

- Dahil sa maliit na hanay ng mga tagubilin ng RISC, ang mga tagakuha ng mataas na antas na wika ay maaaring makagawa ng mas mahusay na code.

- Pinapayagan ng RISC ang kalayaan sa paggamit ng puwang sa microprocessors dahil sa pagiging simple nito.

- Sa halip na gamitin ang Stack, maraming mga processor ng RISC ang gumagamit ng mga rehistro para sa pagpasa ng mga argumento at hinahawakan ang mga lokal na variable.

- Gumagamit lamang ang mga pag-andar ng RISC ng ilang mga parameter, at hindi maaaring gamitin ng mga nagpoproseso ng RISC ang mga tagubilin sa pagtawag, at samakatuwid, gumamit ng isang nakapirming mga tagubilin sa haba na madaling pipeline.

- Ang bilis ng operasyon ay maaaring ma-maximize at ang oras ng pagpapatupad ay maaaring mabawasan.

- Napakaliit na bilang ng mga format ng tagubilin (mas mababa sa apat), ilang bilang ng mga tagubilin (sa paligid ng 150) at ilang mga mode sa pagtugon (mas mababa sa apat) ang kinakailangan.

Mga drawback ng arkitektura ng RISC processor

- Sa pagdaragdag ng haba ng mga tagubilin, tumataas ang pagiging kumplikado para sa mga prosesor ng RISC upang maisagawa dahil sa cycle ng character nito bawat tagubilin.

- Ang pagganap ng mga nagpoproseso ng RISC ay nakasalalay sa karamihan sa tagatala o programmer dahil ang kaalaman sa tagatala ay may pangunahing papel habang kinokonekta ang CISC code sa isang RISC code samakatuwid, ang kalidad ng nabuong code ay nakasalalay sa tagatala.

- Habang itinatakda ang iskedyul ng CISC code sa isang RISC code, na tinukoy bilang isang pagpapalawak ng code, ay tataas ang laki. At, ang kalidad ng pagpapalawak ng code na ito ay muling aasa sa tagatala, at din sa hanay ng tagubilin ng makina.

- Ang unang antas ng cache ng mga nagpoproseso ng RISC ay isang kawalan din ng RISC, kung saan ang mga prosesor na ito ay may malaking memorya ng cache sa chip mismo. Para sa pagpapakain ng mga tagubilin, nangangailangan sila ng napaka mabilis na mga sistema ng memorya .

Arkitektura ng CISC (Komplikadong Itakda ang Computer na Itakda)

Ang pangunahing hangarin ng arkitektura ng CISC processor ay upang makumpleto ang gawain sa pamamagitan ng paggamit ng mas kaunting bilang ng mga linya ng pagpupulong. Para sa hangaring ito, ang processor ay binuo upang magpatupad ng isang serye ng mga pagpapatakbo. Ang pagtuturo ng kumplikadong ay tinatawag ding MULT, na nagpapatakbo mga bangko ng memorya ng isang computer nang direkta nang hindi ginagawa ang tagatala upang maisagawa ang pag-iimbak at pag-load ng mga pagpapaandar.

Arkitektura ng CISC

Mga Tampok ng CISC Architecture

- Upang gawing simple ang arkitektura ng computer, sinusuportahan ng CISC ang microprogramming.

- Ang CISC ay may higit na bilang ng mga paunang natukoy na tagubilin na ginagawang madali ang pagdisenyo at pagpapatupad ng mga wikang mataas na antas.

- Ang CISC ay binubuo ng mas kaunting bilang ng mga rehistro at higit na bilang ng mga mode sa pagtugon, sa pangkalahatan 5 hanggang 20.

- Ang CISC processor ay tumatagal ng magkakaibang oras ng pag-ikot para sa pagpapatupad ng mga tagubilin - mga pag-ikot ng maraming orasan.

- Dahil sa kumplikadong hanay ng pagtuturo ng CISC, ang diskarteng pipelining ay napakahirap.

- Ang CISC ay binubuo ng higit pang bilang ng mga tagubilin, sa pangkalahatan mula 100 hanggang 250.

- Ang mga espesyal na tagubilin ay ginagamit nang napakabihirang.

- Ang mga pagpapatakbo sa memorya ay manipulahin ng mga tagubilin.

Mga kalamangan ng arkitektura ng CISC

- Ang bawat tagubilin sa wika ng makina ay naka-grupo sa isang tagubilin sa microcode at naisagawa nang naaayon, at pagkatapos ay naka-imbak na built in sa memorya ng pangunahing processor, na tinukoy bilang pagpapatupad ng microcode.

- Tulad ng memorya ng microcode ay mas mabilis kaysa sa pangunahing memorya, ang set ng pagtuturo ng microcode ay maaaring ipatupad nang walang malaking pagbawas ng bilis sa matitigas na wired na pagpapatupad.

- Ang buong bagong hanay ng pagtuturo ay maaaring mapangasiwaan sa pamamagitan ng pagbabago ng disenyo ng micro program.

- Ang CISC, ang bilang ng mga tagubiling kinakailangan upang magpatupad ng isang programa ay maaaring mabawasan sa pamamagitan ng pagbuo ng mayamang mga hanay ng tagubilin at maaari ring gawin upang magamit nang mas mahusay ang mabagal na pangunahing memorya.

- Dahil sa superset ng mga tagubilin na binubuo ng lahat ng mga naunang tagubilin, ginagawang madali ang micro coding.

Mga drawbacks ng CISC

- Ang dami ng oras ng orasan na kinunan ng iba't ibang mga tagubilin ay magkakaiba - dahil dito - mabagal ang pagganap ng makina.

- Ang pagtuturo ng pagiging kumplikado at ang hardware ng chip ay tumataas habang ang bawat bagong bersyon ng processor ay binubuo ng isang subset ng mga naunang henerasyon.

- 20% lamang ng mga mayroon nang mga tagubilin ang ginagamit sa isang tipikal na kaganapan sa pagprograma, kahit na maraming mga dalubhasang tagubilin na mayroon na kahit na hindi madalas ginagamit.

- Ang mga kondisyonal na code ay itinakda ng mga tagubilin sa CISC bilang isang epekto sa bawat tagubilin na tumatagal ng oras para sa setting na ito - at, habang binabago ng kasunod na tagubilin ang mga bits ng code ng kundisyon - kaya, dapat suriin ng tagatala ang mga bits ng code ng kondisyon bago ito mangyari.

RISC vs. CISC

- Ang mga pag-aksaya ng pag-ikot ay maaaring mapigilan ng programmer sa pamamagitan ng pag-alis ng hindi kinakailangang code sa RISC, ngunit, habang ginagamit ang CISC code ay humahantong sa pag-aaksaya ng mga siklo dahil sa pagiging mabisa ng CISC.

- Sa RISC, ang bawat tagubilin ay inilaan upang maisagawa ang isang maliit na gawain tulad nito, upang maisagawa ang isang kumplikadong gawain, maraming maliliit na tagubilin ang ginagamit nang magkasama, samantalang kakaunti lamang ang mga tagubilin na kinakailangan upang gawin ang parehong gawain gamit ang CISC - dahil may kakayahang magsagawa ng kumplikadong gawain dahil ang mga tagubilin ay katulad ng isang code na may mataas na wika.

- Karaniwang ginagamit ang CISC para sa mga computer habang ang RISC ay ginagamit para sa mga smart phone, tablet at iba pang mga elektronikong aparato.

Ang sumusunod na pigura ay nagpapakita ng higit na pagkakaiba sa pagitan ng RISC at CISC

RISC vs. CISC

Kaya, tinatalakay ng artikulong ito ang tungkol sa mga tampok na arkitektura ng RISC at CISC ng mga kalamangan sa arkitektura ng RISC at CISC at mga drawbacks ng RISC at CISC, at mga pagkakaiba sa pagitan ng mga arkitektura ng RISC at CISC na may isang maikling ideya. Para sa karagdagang impormasyon tungkol sa mga arkitektura ng RISC at CISC, mangyaring i-post ang iyong mga query sa pamamagitan ng pagkomento sa ibaba.

Mga Kredito sa Larawan:

- Hanay ng tagubilin ng Proseso ng arstechnica

- RISC Arkitektura ni lsi-patimpalak

- RISC kumpara sa CISC ni csarigyanment