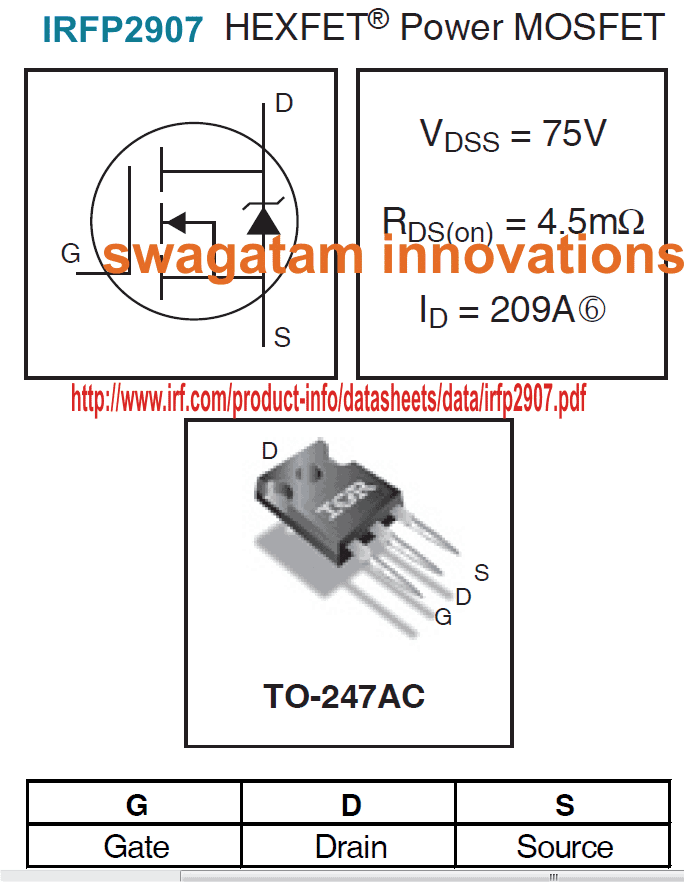

Sa post na ito tinatalakay namin ang mga rating ng avalanche ng MOSFET, at natututunan kung paano maunawaan nang tama ang rating na ito sa datasheet, kung paano sinubukan ng parameter ang tagagawa, at mga hakbang upang protektahan ang MOSFET mula sa hindi pangkaraniwang bagay na ito.

Ang parameter ng avalanche ay hindi lamang nakakatulong upang mapatunayan ang kawalang-kilos ng mga aparato, bukod pa rito ay nakakatulong sa pag-filter ng mga mahihinang MOSFET o sa mga mas madaling kapitan o nasa peligro ng isang pagkasira.

Ano ang MOSFET Rating ng Avalanche

Ang MOSFET avalanche rating ay ang maximum na matatagalan na enerhiya (millijoule) na makatiis ang isang MOSFET, kapag ang boltahe na pinagmulan ng alisan ng tubig ay lumampas sa maximum na limitasyon ng boltahe ng breakdown (BVDSS).

Karaniwang nangyayari ang hindi pangkaraniwang bagay na ito sa MOSFET switching circuit na may inductive load sa buong drain terminal.

Sa mga Panahon ng ON ng mga switching cycle, singil ng inductor, at sa mga panahon ng OFF ang inductor ay naglalabas ng nakaimbak na enerhiya sa anyo ng back EMF sa kabuuan ng source-drain ng MOSFET.

Dumadaan ang pabalik na boltahe na ito sa pamamagitan ng diode ng katawan ng MOSFET, at kung ang halaga nito ay lumagpas sa maximum na limitasyong kinakaya ng aparato, nagiging sanhi ng matinding init na bubuo sa loob ng aparato na nagdudulot ng pinsala o isang permanenteng pinsala sa aparato.

Kailan ipinakilala ang MOSFET Avalanche

Ang kasalukuyang parameter na Avalanche Energy at UIS (hindi naka-clamp na inductive switching) ay kasalukuyang hindi kasama sa mga datosheet ng MOSFET bago ang 1980s.

At iyon ay noong nagbago ito sa hindi lamang isang detalye ng datasheet, ngunit isang parameter na sinimulan ng hiniling ng maraming mga mamimili na masubukan ang FET bago ipasa ang aparato para sa produksyon, lalo na, kung ang MOSFET ay dinisenyo para sa supply ng kuryente o paglipat ng mga pagpapatupad.

Samakatuwid pagkatapos lamang ng 1980s na ang parameter ng avalanche ay nagsimulang lumitaw sa mga datasheet, at pagkatapos ay nagsimulang maunawaan ng mga technician ng promosyon na mas malaki ang rating ng avalanche, mas naging kumpetisyon ang aparato.

Sinimulan ng mga inhinyero ang pagtukoy ng mga diskarte upang mag-eksperimento sa parameter sa pamamagitan ng pag-aayos ng ilan sa mga variable nito, na ginamit para sa proseso ng pagsubok.

Sa pangkalahatan, sa mas malaki ang lakas ng avalanche, mas matibay at malakas ang MOSFET. Samakatuwid mas malaking rating ng avalanche, kumakatawan sa mas malakas na mga katangian ng MOSFET.

Karamihan sa mga datosheet ng FET ay karaniwang magkakaroon ng parameter ng avalanche na kasama sa kanilang Talaan ng Maximum Ratings, na maaaring direktang makita sa pahina ng pagpasok ng sheet ng data. Lalo na, maaari mong tingnan ang mga parameter dito na nakasulat bilang Avalanche Kasalukuyan at Avalanche Energy, Eas.

Samakatuwid, sa mga datasheet ang MOSFET Avalanche Energy ay ipinakita bilang dami ng enerhiya na maaring tiisin ng MOSFET habang isasailalim ito sa avalanche test, o kapag tumawid ang pinakamataas na rating ng boltahe ng breakdown ng MOSFET.

Kasalukuyang Avalanche at UIS

Ang maximum na rate ng boltahe ng pagkasira ng boltahe ay natutukoy sa pamamagitan ng Kasalukuyang Pagsubok ng Avalanche, na nagawa sa pamamagitan ng isang hindi nasisiksik na Inductive Switching na pagsubok o ang pagsubok ng UIS.

Samakatuwid kapag pinag-usapan ng mga inhinyero ang tungkol sa kasalukuyang UIS, maaari silang tumutukoy sa Kasalukuyang Avalanche.

Isinasagawa ang isang walang siksik na inductive switching test upang malaman ang kasalukuyang at dahil doon ang lakas ng avalanche na maaaring magpalitaw sa pagkabigo ng MOSFET.

Tulad ng nabanggit nang mas maaga, ang mga magnitude o rating na ito ay lubos na nakasalalay sa mga pagtutukoy ng pagsubok, lalo na, ang halaga ng inductor na inilapat sa oras ng pagsubok.

Test setup

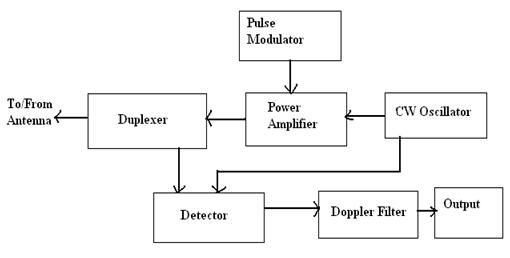

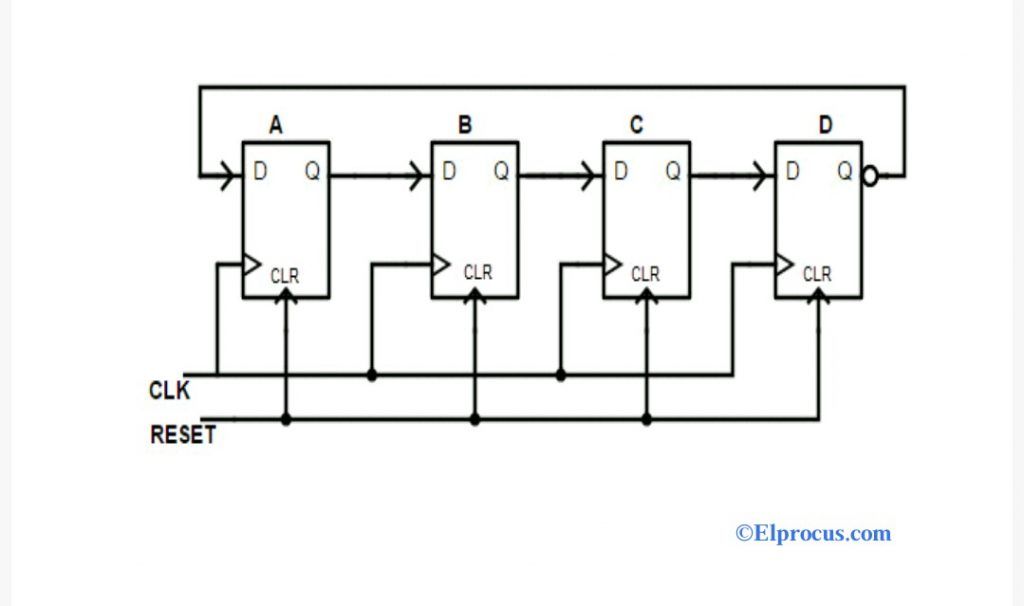

Ang sumusunod na diagram ay nagpapakita ng isang karaniwang pag-set up ng circuit ng pagsubok ng UIS.

Sa gayon nakikita namin ang isang supply ng boltahe sa serye na may isang inductor, L, na kung saan ay din sa serye na may MOSFET sa ilalim ng pagsubok. Maaari rin kaming makakita ng isang driver ng gate para sa FET na ang output ay sunud-sunod na may isang FET gate resistor R.

Sa imahe sa ibaba, nalaman namin, ang aparato ng LTC55140 controller, na ginagamit sa Texas Instrument lab upang suriin ang mga katangian ng UIS ng FET.

Ang katangian ng UIS na kasunod ay tumutulong hindi lamang upang malaman ang rating ng FET datasheet, kundi pati na rin ang halagang ginamit upang i-scan ang FET sa huling pamamaraan ng pagsubok.

Pinapayagan ng tool ang pag-tweak ng halaga ng load inductor mula 0.2 hanggang 160 millihenry. Pinapayagan nito ang pag-aayos ng boltahe ng alisan ng tubig ng MOSFET sa ilalim ng pagsubok mula 10 hanggang 150 volts.

Ito, bilang isang resulta ay ginagawang posible upang mai-screen kahit na ang mga FET na na-rate upang mahawakan lamang ang boltahe ng boltahe na 100 boltahe. At, naging posible na mag-apply ng mga daloy ng agos mula 0.1 hanggang 200 amps. At ito ang kasalukuyang saklaw ng UIS kung saan maaaring tiisin ng FET sa panahon ng pamamaraan ng pagsubok.

Bilang karagdagan pinapayagan ng tool ang pagtatakda ng iba't ibang mga saklaw ng mga temperatura ng kaso ng MOSFET, mula -55 hanggang +150 degree.

Mga Pamamaraan sa Pagsubok

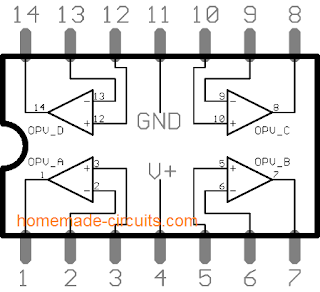

Ang karaniwang pagsubok sa UIS ay ipinatupad sa pamamagitan ng 4 na yugto, tulad ng inilalarawan sa sumusunod na imahe:

Ang unang yugto ay binubuo ng pre-leakage test, kung saan ang supply boltahe ay bias ang FET na alisan ng tubig. Sa panimula, ang ideya dito ay upang subukan upang matiyak na ang FET ay gumaganap sa normal na inaasahang paraan.

Kaya, sa unang yugto ang FET ay gaganapin nakasara. Pinapanatili nito ang pag-block ng boltahe ng supply sa mga daim-emitter terminal, nang hindi nakakaranas ng anumang uri ng labis na kasalukuyang pagtulo na dumadaloy dito.

Sa pangalawang yugto, na kilala bilang Avalanche Kasalukuyang ramp up, ang FET ay nakabukas SA, na sanhi ng pagbagsak ng boltahe ng kanal. Nagreresulta ito sa kasalukuyang tumaas nang dahan-dahan sa pamamagitan ng inductor na may pare-pareho na di / dt. Kaya karaniwang sa yugtong ito, pinapayagan ang inductor na singilin.

Sa ikatlong yugto, ang aktwal na pagsubok ng avalanche ay isinasagawa, kung saan ang FET ay halos napailalim sa avalanche. Sa yugtong ito ang FET ay naka-off sa pamamagitan ng pag-aalis ng bias ng gate nito. Nagreresulta ito sa isang napakalaking di / dt na dumadaan sa inductor, na sanhi ng boltahe ng FET na alisan ng tubig na mag-shoot ng mataas sa itaas ng limitasyon ng boltahe ng FET.

Pinipilit nito ang FET na dumaan sa pag-akyat ng avalanche. Sa prosesong ito, ang FET ay sumisipsip ng buong enerhiya na nabuo ng inductor, at mananatiling nakasara, hanggang sa maipatupad ang ika-4 na yugto, na kinasasangkutan ng post leakage test

Sa ika-4 na yugto na ito ang FET ay muling napailalim sa isang paulit-ulit na pagsubok ng avalanche, upang matiyak kung ang MOSFET ay kumikilos pa rin nang normal o hindi. Kung gagawin ito, ang FET ay itinuturing na nakapasa sa pagsubok sa avalanche.

Susunod, ang FET ay kailangang dumaan sa pagsubok sa itaas nang maraming beses, kung saan ang antas ng boltahe ng UIS ay unti-unting nadagdagan sa bawat pagsubok, hanggang sa antas kung saan hindi makatiis ang MOSFET at nabigo ang post-leakage test. At ang kasalukuyang antas na ito ay nabanggit na pinakamataas na kasalukuyang UIS ng MOSFET na walang kakayahang manatili.

Kinakalkula ang MOSFET Avalanche Energy

Kapag ang maximum na UIS kasalukuyang kakayahan sa paghawak ng MOSFET ay napagtanto, kung saan nasisira ang aparato, nagiging mas madali para sa mga inhinyero na tantyahin ang dami ng enerhiya na nawala sa pamamagitan ng FET sa panahon ng proseso ng avalanche.

Ipagpalagay, ang buong enerhiya na nakaimbak sa inductor ay nawala sa MOSFET habang ang avalanche, ang lakas ng enerhiya na ito ay maaaring matukoy gamit ang sumusunod na pormula:

AYAS= 1 / 2L x INGdalawa

AYASay nagbibigay sa amin ng lakas ng enerhiya na nakaimbak sa loob ng inductor, na katumbas ng 50% ng halaga ng inductance na pinarami ng kasalukuyang kuwadro, na dumadaloy sa pamamagitan ng inductor.

Dagdag dito, napansin na habang ang halaga ng inductor ay nadagdagan, ang dami ng kasalukuyang responsable para sa pagkasira ng MOSFET na talagang nabawasan.

Gayunman, ang pagtaas ng laki ng inductor na ito ay nag-offset sa pagbawas na ito sa kasalukuyang pormula sa itaas na enerhiya sa isang paraan na literal na tumataas ang halaga ng enerhiya.

Enerhiya ng Avalanche o Kasalukuyang Avalanche?

Ito ang dalawang mga parameter, na maaaring malito ang mga mamimili, habang sinusuri ang isang MOSFET datasheet para sa avalanche rating.

Copyright © Texas Instruments Incorporated

Marami sa mga tagagawa ng MOSFET ay sadyang sinubukan ang MOSFET na may mas malaking mga inductor, upang maipagmamalaki ang isang mas malaking lakas ng avalanche na lakas, na lumilikha ng isang impression na ang MOSFET ay nasubok para sa mapaglabanan ang malalaking mga enerhiya ng avalanche, at samakatuwid ay may nadagdagang tibay sa avalanche.

Ngunit ang pamamaraan sa itaas ng paggamit ng mas malaking inductor ay mukhang nakaliligaw, iyon ang eksaktong dahilan kung bakit ang mga inhinyero ng Texas Instruments ay sumusubok na may mas maliit na inductance sa pagkakasunud-sunod ng 0.1 mH, upang ang MOSFET sa ilalim ng pagsubok ay napailalim sa mas mataas na kasalukuyang antas ng Avalanche at matinding pagkasira ng stress.

Kaya, sa mga datasheet, hindi ito ang enerhiya ng Avalanche, sa halip na kasalukuyang Avalanche na dapat ay mas malaki sa dami, na nagpapakita ng mas mahusay na pagkamagaspang ng MOSFET.

Ginagawa nitong pangwakas ang pangwakas na pagsubok at nagbibigay-daan sa pag-filter ng maraming mga mahina na MOSFET hangga't maaari.

Ang halaga ng pagsubok na ito ay hindi lamang ginamit bilang pangwakas na halaga bago ang FET layout ay naipasa para sa paggawa, ngunit ito rin ang halaga na ipinasok sa datasheet.

Sa susunod na hakbang, ang halaga ng pagsubok sa itaas ay derated ng 65%, upang ang end user ay makakakuha ng isang mas malawak na margin ng pagpapaubaya para sa kanilang mga MOSFET.

Halimbawa, kung ang nasubok na kasalukuyang avalanche ay 125 Amps, ang pangwakas na halaga na ipinasok sa datasheet ay magiging 81 Amps, pagkatapos ng derating.

Kasalukuyang MOSFET Avalanche kumpara sa Oras na Ginugol sa Avalanche

Ang isa pang parameter na nauugnay sa power MOSFET at nabanggit sa mga datasheet, lalo na para sa MOSFET na idinisenyo para sa paglipat ng mga aplikasyon ay ang Avalanche Kasalukuyang Kakayahan kumpara sa Oras na Ginugol sa Avalanche. Ang parameter na ito ay karaniwang ipinapakita patungkol sa temperatura ng kaso ng MOSFET sa 25 degree. Sa panahon ng pagsubok ang kaso temperatura ay nadagdagan sa 125 degree.

Sa sitwasyong ito ang temperatura ng kaso ng MOSFET ng MOSFET ay napakalapit sa aktwal na temperatura ng kantong ng silicon die ng MOSFET.

Sa pamamaraang ito habang nadaragdagan ang temperatura ng junction ng aparato, maaari mong asahan na makita ang isang tiyak na halaga ng pagkasira na medyo normal? Gayunpaman, kung ang resulta ay nagpapakita ng isang mataas na antas ng pagkasira, maaaring ipahiwatig ang mga palatandaan ng isang likas na mahina na aparato ng MOSFET.

Samakatuwid mula sa isang pananaw sa disenyo, isang pagtatangka ay ginawa upang matiyak na ang pagkasira ng katawan ay hindi lalampas sa 30% para sa pagtaas ng temperatura ng kaso mula 25 hanggang 125 degree.

Paano Protektahan ang MOSFET mula sa Kasalukuyang Avalanche

Tulad ng natutunan namin mula sa mga talakayan sa itaas, ang avalanche sa MOSFETs ay binuo dahil sa mataas na boltahe na inductive back na EMF na lumilipat sa diode ng katawan ng MOSFET.

Kung ang pabalik na boltahe ng EMF na ito ay lumampas sa maximum na rating ng body diode, sanhi ng matinding pagbuo ng init sa aparato at kasunod na pinsala.

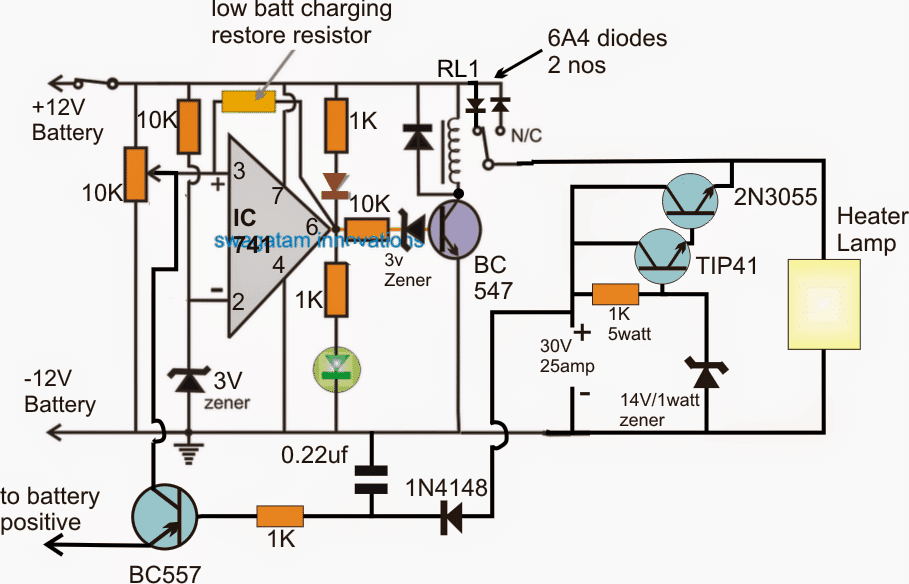

Ipinapahiwatig nito na kung ang inductive EMF boltahe ay pinapayagan na dumaan sa isang panlabas na naaangkop na na-rate bypass diode, sa buong drain-emitter ng FET ay maaaring makatulong na maiwasan ang hindi pangkaraniwang bagay na avalanche.

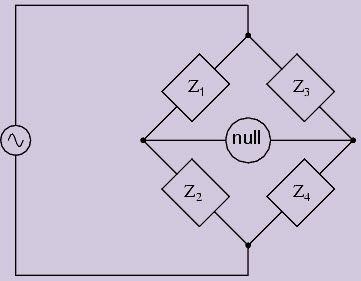

Ang sumusunod na diagram ay nagmumungkahi ng karaniwang disenyo ng pagdaragdag ng isang panlabas na diode ng emitter para sa pagpapalakas ng panloob na diode ng katawan ng MOSFET.

Kagandahang-loob: MOSFET Avalanche

Nakaraan: Ang pag-convert ng Nasayang na Spark Ignition sa Sequential Spark, para sa Mataas na Kakayahang pagkasunog Susunod: Simpleng Online UPS Circuit