Para sa pagpapatupad ng isang programa sa computer, kinakailangan nito ang magkasabay na pagtatrabaho ng higit sa isang bahagi ng isang computer. Halimbawa, Mga nagpoproseso - pagbibigay ng kinakailangang impormasyon sa pagkontrol, mga address… atbp, mga bus - upang ilipat ang impormasyon at data sa at mula sa memorya sa mga I / O na aparato ... atbp. Ang kagiliw-giliw na kadahilanan ng system ay ang magiging paraan nito sa paghawak ng paglipat ng impormasyon sa mga processor, memorya at I / O na mga aparato. Karaniwan, kinokontrol ng mga processor ang lahat ng proseso ng paglilipat ng data, mula mismo sa pagpapasimula ng paglipat sa pag-iimbak ng data sa patutunguhan. Nagdaragdag ito ng pagkarga sa processor at kadalasang nananatili ito sa perpektong estado, sa gayon ay nababawasan ang kahusayan ng system. Upang mapabilis ang paglipat ng data sa pagitan ng mga I / O aparato at memorya, ang DMA controller ay kumikilos bilang master ng istasyon. Naglilipat ang DMA controller ng data na may kaunting interbensyon ng processor.

Ano ang isang DMA Controller?

Ang katagang DMA ay nangangahulugang direktang pag-access sa memorya. Ang aparato ng hardware na ginamit para sa direktang pag-access sa memorya ay tinatawag na DMA controller. DMA ang controller ay isang control unit , bahagi ng I / O aparato interface ng circuit , na maaaring maglipat ng mga bloke ng data sa pagitan ng mga aparato ng I / O at pangunahing memorya na may kaunting interbensyon mula sa processor.

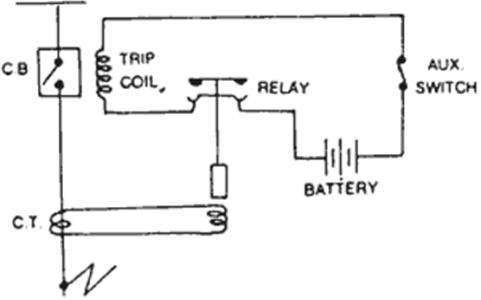

DMA Controller Diagram sa Computer Architecture

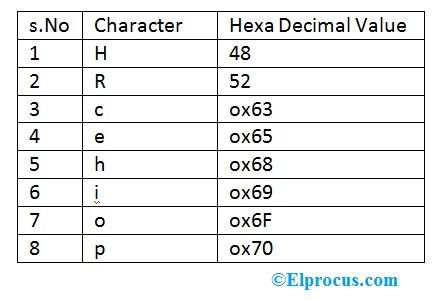

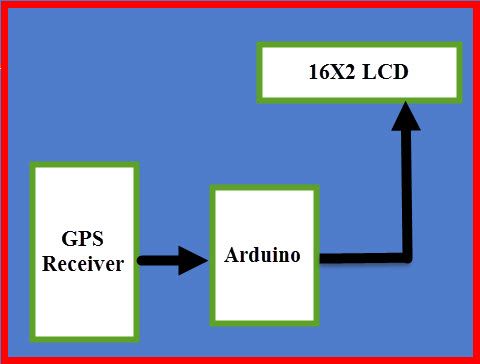

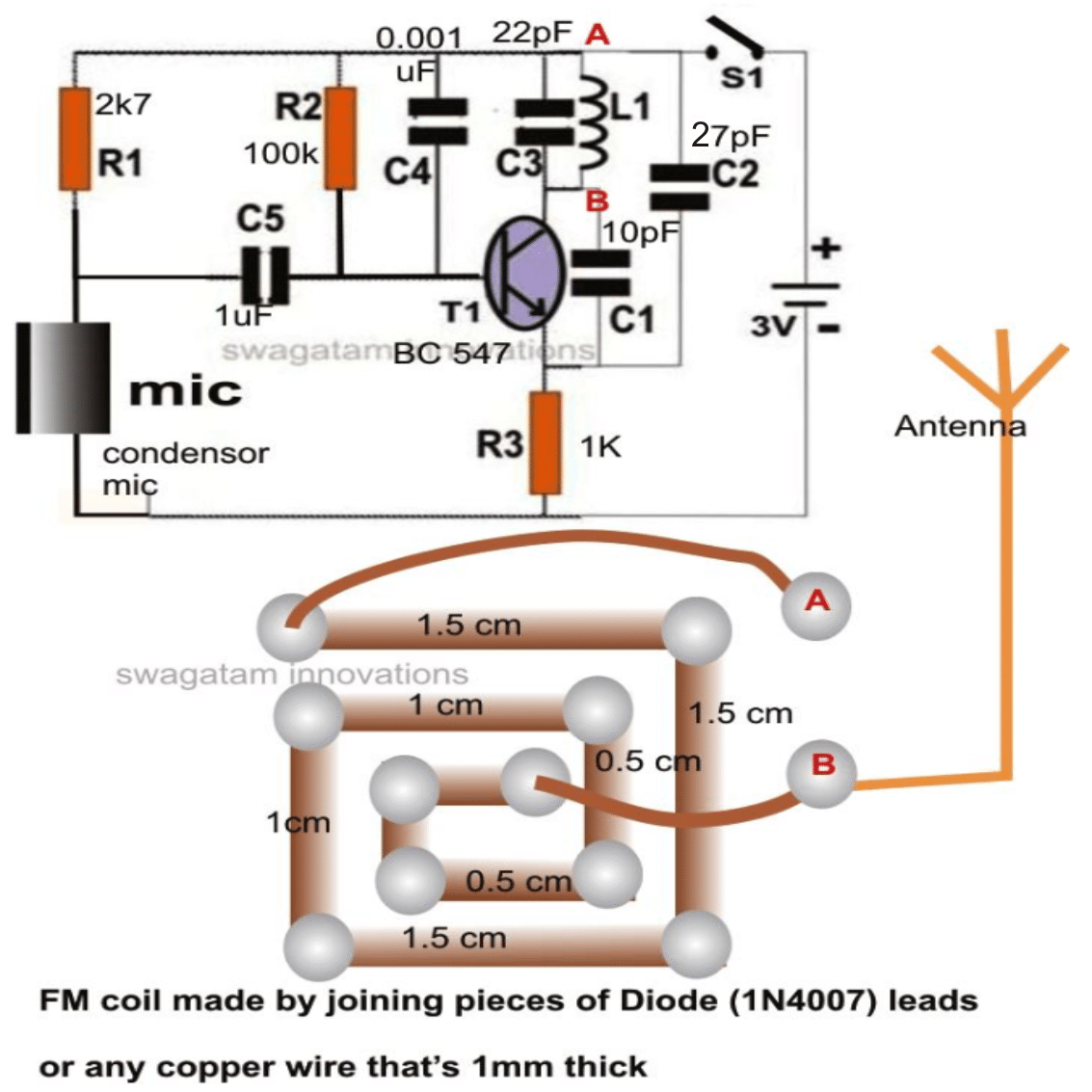

Nagbibigay ang DMA controller ng isang interface sa pagitan ng bus at mga input-output na aparato. Kahit na naglilipat ito ng data nang walang interbensyon ng processor, kinokontrol ito ng processor. Pinasimulan ng processor ang DMA controller sa pamamagitan ng pagpapadala ng panimulang address, Bilang ng mga salita sa bloke ng data at direksyon ng paglipat ng data .i.e. mula sa mga I / O aparato hanggang sa memorya o mula sa pangunahing memorya hanggang sa mga I / O na aparato. Mahigit sa isang panlabas na aparato ang maaaring konektado sa DMA controller.

DMA sa Computer Architecture

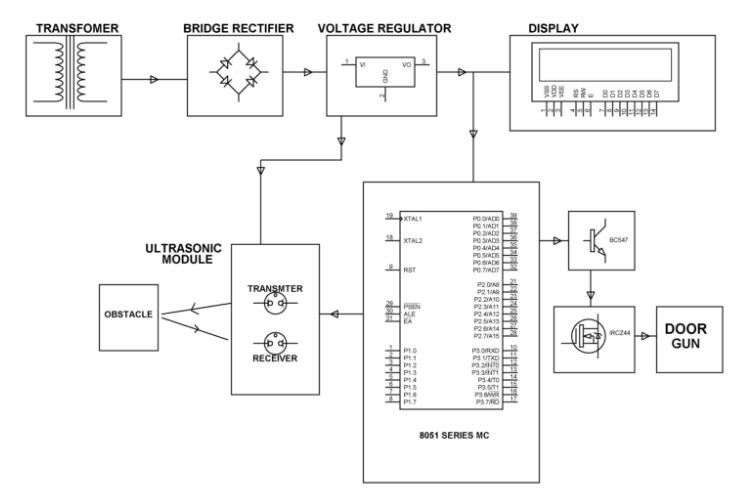

Naglalaman ang DMA controller ng isang unit ng address, para sa pagbuo ng mga address at pagpili ng I / O aparato para sa paglipat. Naglalaman din ito ng control unit at bilang ng data para sa pagpapanatili ng bilang ng bilang ng mga bloke na inilipat at nagpapahiwatig ng direksyon ng paglipat ng data. Kapag nakumpleto ang paglipat, ipinapaalam ng DMA sa processor sa pamamagitan ng pagtaas ng isang nakakagambala. Ang tipikal na diagram ng block ng DMA controller ay ipinapakita sa figure sa ibaba.

Karaniwang Block Diagram ng DMA Controller

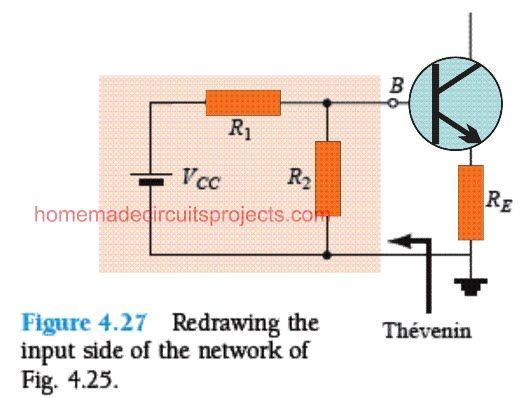

Paggawa ng DMA Controller

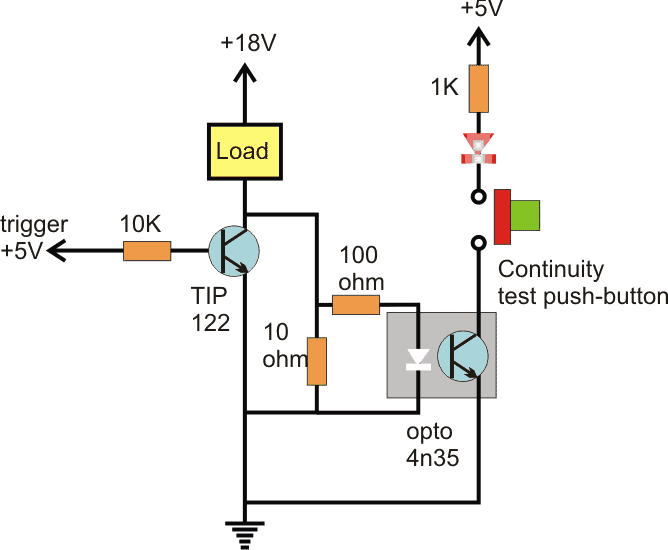

Ang DMA controller ay kailangang ibahagi ang bus sa processor upang magawa ang paglipat ng data. Ang aparato na humahawak ng bus sa isang naibigay na oras ay tinatawag na bus master. Kapag ang isang paglipat mula sa I / O aparato sa memorya o vice talata ay dapat gawin, ihinto ng processor ang pagpapatupad ng kasalukuyang programa, dagdagan ang programa counter, ilipat ang data sa paglipas ng stack pagkatapos ay nagpapadala ng isang DMA select signal sa DMA controller sa address bus.

Kung ang DMA controller ay libre, hinihiling nito ang kontrol ng bus mula sa processor sa pamamagitan ng pagtaas ng signal ng paghiling ng bus. Ibinibigay ng Processor ang bus sa controller sa pamamagitan ng pagtaas ng signal ng pagbibigay ng bus, ngayon ang DMA controller ay ang bus master. Sinimulan ng processor ang DMA controller sa pamamagitan ng pagpapadala ng mga memory address, bilang ng mga bloke ng data na maililipat at direksyon ng paglilipat ng data. Matapos italaga ang gawain sa paglilipat ng data sa DMA controller, sa halip na maghintay nang perpekto hanggang sa makumpleto ang paglipat ng data, ipagpatuloy ng processor ang pagpapatupad ng programa pagkatapos makuha ang mga tagubilin mula sa stack.

Paglipat Ng Data sa Computer Ng DMA Controller

Ang DMA controller ay mayroon nang ganap na kontrol ng mga bus at maaaring makipag-ugnay nang direkta sa memorya at mga I / O na aparato na walang hiwalay sa CPU. Ginagawa nitong paglilipat ng data alinsunod sa mga tagubilin sa kontrol na natanggap ng processor. Matapos makumpleto ang paglilipat ng data, hindi pinapagana nito ang signal ng paghiling ng bus at hindi pinagana ng CPU ang signal ng pagbibigay ng bus sa gayong paglipat ng kontrol ng mga bus sa CPU.

Kapag nais ng isang I / O aparato na simulan ang paglipat pagkatapos ay nagpapadala ito ng isang senyas ng kahilingan ng DMA sa DMA controller, kung saan kinikilala ng controller kung libre ito. Pagkatapos ang kahilingan ng controller sa processor para sa bus, pagtaas ng signal ng kahilingan ng bus. Matapos matanggap ang senyas ng pagbibigay ng bus inililipat nito ang data mula sa aparato. Para sa n-channel DMA controller n bilang ng mga panlabas na aparato ay maaaring konektado.

Inililipat ng DMA ang data sa tatlong mga mode na kasama ang mga sumusunod.

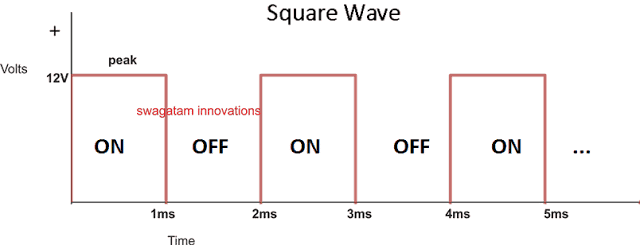

sa) Burst Mode : Sa mode na ito, ibibigay ng DMA ang mga bus sa CPU pagkatapos lamang makumpleto ang buong paglilipat ng data. Samantala, kung kinakailangan ng CPU ang bus kailangang manatiling perpekto at maghintay para sa paglilipat ng data.

b) Cycle Stealing Mode : Sa mode na ito, binibigyan ng DMA ng kontrol ang mga bus sa CPU pagkatapos ilipat ang bawat byte. Patuloy itong naglalabas ng isang kahilingan para sa kontrol ng bus, ginagawa ang paglipat ng isang byte at ibabalik ang bus. Sa pamamagitan ng CPU na ito ay hindi na kailangang maghintay ng mahabang panahon kung kailangan nito ng isang bus para sa mas mataas na pangunahing gawain.

c) Transparent Mode: Dito, inililipat lamang ng DMA ang data kapag ang CPU ay nagpapatupad ng tagubilin na hindi nangangailangan ng paggamit ng mga bus.

8237 DMA Controller

- Ang 8237 ay mayroong 4 na I / O channel kasama ang kakayahang umangkop ng pagtaas ng bilang ng mga channel.

- Ang bawat channel ay maaaring mai-program nang paisa-isa at mayroong isang 64k address at kakayahan sa data.

- Ang bloke ng kontrol sa tiyempo, bloke ng control ng utos ng Programa, ang Priority Encoder Block ay ang tatlong pangunahing mga bloke ng 8237A.

- Ang panloob na tiyempo at panlabas na mga signal ng kontrol ay hinihimok ng block ng kontrol ng tiyempo.

- Ang iba't ibang mga utos na ibinigay ng microprocessor sa DMA ay na-decode ng program control control block.

- Aling channel ang dapat bigyan ng pinakamataas na priyoridad ay napagpasyahan ng priyoridad encoder bloke .

Ang 8237A ay mayroong 27 panloob na mga rehistro.

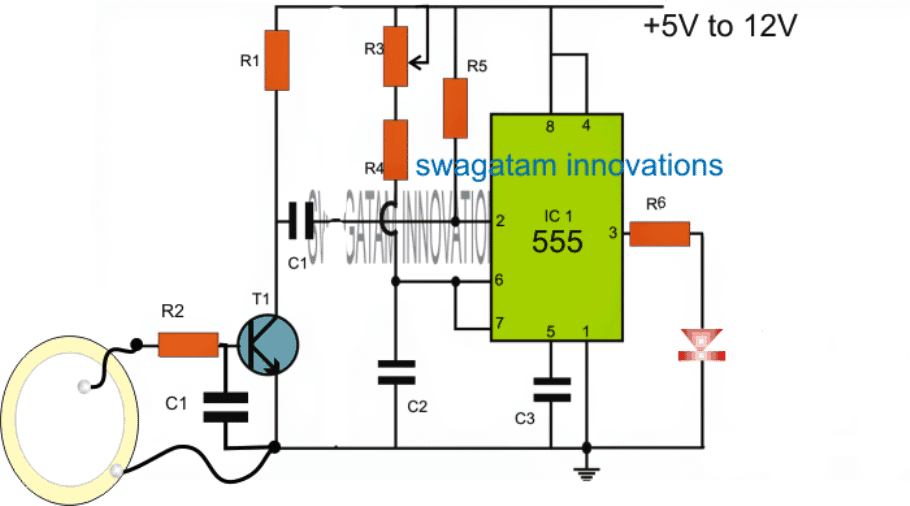

Ang 8237A ay nagpapatakbo sa dalawang siklo- Perpektong pag-ikot at aktibong pag-ikot, kung saan ang bawat pag-ikot ay naglalaman ng 7 magkakahiwalay na estado na binubuo ng isang oras ng orasan bawat isa.

S0- Ang unang estado, kung saan humiling ang tagakontroler para sa bus at naghihintay para sa pagkilala mula sa processor.

Ang S1, S2, S3, S4 ay tinawag na mga gumaganang estado ng 8237A kung saan nagaganap ang tunay na paglipat ng data. Kung kailangan ng mas maraming oras para sa paglipat ng mga estado ng paghihintay ay idinagdag ang SW sa pagitan ng mga estadong ito.

Para sa memorya –to- memorya ng paglilipat ay kailangang gawin ang mga transfer-mula-memorya at mga transfer-to-memory. Walong estado ang kinakailangan para sa solong paglipat. Ang unang apat na estado na may mga subscripts na S11, S12, S13, S14 ay ang read-from-memory transfer at ang susunod na apat na S21, S22, S23, S24 ay para sa transfer-to-memory transfer.

Ang DMA ay pumupunta sa ideal na estado kapag walang channel na humihiling ng serbisyo at isagawa ang estado ng SI. Ang SI ay isang hindi aktibong estado kung saan ang DMA ay hindi aktibo hanggang sa makatanggap ito ng isang kahilingan. Sa estado na ito, ang DMA ay nasa kondisyon ng programa kung saan maaaring iprograma ng processor ang DMA.

Kapag ang DMA ay nasa perpektong estado at walang karagdagang mga kahilingan sa channel, naglalabas ito ng isang signal ng HRQ sa processor at pumapasok sa Aktibong estado kung saan maaari nitong simulan ang paglipat ng data alinman sa pamamagitan ng burst mode, cycle steal mode o transparent mode.

8237 Pin Diagram

8257 DMA Controller

Kapag ipinares sa solong Intel 8212 I / O port device, ang 8257 DMA controller ay bumubuo ng isang kumpletong 4 na channel Controller ng DMA . Sa pagtanggap ng isang kahilingan sa paglipat ang 8257 controller-

- Kinukuha ang kontrol sa system bus mula sa processor.

- Kinikilala ang peripheral na konektado sa pinakamataas na channel ng priyoridad.

- Ang hindi gaanong makabuluhang mga piraso ng address ng memorya ay inililipat sa mga linya ng address na A0-A7 ng system bus.

- Ang pinaka makabuluhan 8 bit ng memorya ng address ay hinihimok sa 8212 I / O port sa pamamagitan ng mga linya ng data.

- Bumubuo ng naaangkop na mga signal ng kontrol para sa paglipat ng data sa pagitan ng mga peripheral at address na lokasyon ng memorya.

- Kapag ang tinukoy na bilang ng mga byte ay inililipat, ipaalam ng controller ang pagtatapos ng paglipat ng CPU sa pamamagitan ng pag-aktibo ng output ng bilang ng terminal (TC).

Para sa bawat channel 8257 naglalaman ng dalawa 16-bit na rehistro - 1) rehistro ng DMA address at 2) Pagrehistro ng bilang ng terminal, na dapat isimuno bago ang isang channel ay pinagana. Ang address ng unang lokasyon ng memorya na maa-access ay na-load sa rehistro ng DMA address. Ang mas mababang order na 14 na piraso ng halagang na-load sa pagrehistro ng bilang ng terminal ay nagpapahiwatig ng bilang ng mga siklo ng DMA na minus isa bago ang pag-aktibo ng output ng bilang ng Terminal. Ang uri ng pagpapatakbo para sa isang channel ay ipinahiwatig ng pinakamahalagang dalawang piraso ng rehistro ng bilang ng Terminal.

8257 Pin Diagram

Mga Kalamangan at Kalamangan ng DMA Controller

Ang mga kalamangan at kawalan ng DMA controller ay kasama ang sumusunod.

Mga kalamangan

- Pinapabilis ng DMA ang mga pagpapatakbo ng memorya sa pamamagitan ng pag-bypass sa paglahok ng CPU.

- Ang labis na karga sa CPU ay nababawasan.

- Para sa bawat paglipat, ilang bilang lamang ng mga cycle ng orasan ang kinakailangan

Mga Dehado

- Ang problema sa pagkakaugnay ng cache ay makikita kapag ginamit ang DMA para sa paglilipat ng data.

- Pinapataas ang presyo ng system.

DMA ( Direktang Pag-access sa Memorya ) Ang controller ay ginagamit sa mga graphic card, network card, sound card atbp… Ginagamit din ang DMA para sa intra-chip transfer sa mga multi-core na processor. Pagpapatakbo sa isa sa tatlong mga mode nito, maaaring mabawasan ng DMA ang load ng processor. Alin sa mga mode ng DMA ang iyong pinagtulungan? Alin sa mode na itinuturing mong mas epektibo?