Ang patlang-epekto transistor Ang (FET) ay isang elektronikong aparato kung saan ang a electric field ay ginagamit upang makontrol ang daloy ng kasalukuyang. Upang maipatupad ito ang isang potensyal na pagkakaiba ay inilalapat sa buong gate at mga terminal ng pinagmulan ng aparato, na binabago ang kondaktibiti sa pagitan ng mga drain at source terminal na nagdudulot ng isang kinokontrol na kasalukuyang dumaloy sa mga terminal na ito.

Ang mga FET ay tinawag unipolar transistors sapagkat ang mga ito ay idinisenyo upang mapatakbo bilang mga aparato na may isang kasamang carrier. Mahahanap mo ang iba't ibang mga uri ng mga field effect transistor na magagamit.

Simbolo

Ang mga graphic na simbolo para sa n-channel at p-channel JFET ay maaaring mailarawan sa mga sumusunod na numero.

Malinaw mong mapapansin na ang mga marka ng arrow na tumuturo papasok para sa n-channel na aparato upang ipahiwatig ang direksyon kung saan akoGAng (kasalukuyang gate) ay dapat na dumaloy kapag ang p-n junction ay na-bias na pasulong.

Sa kaso ng isang aparato ng p-channel ang mga kundisyon ay magkapareho maliban sa pagkakaiba sa direksyon ng simbolo ng arrow.

Pagkakaiba sa pagitan ng FET at BJT

Ang field-effect transistor (FET) ay isang aparato na tatlong-terminal na idinisenyo para sa isang malawak na hanay ng mga aplikasyon ng circuit na umakma, sa isang mahusay na antas, ng mga transistor ng BJT.

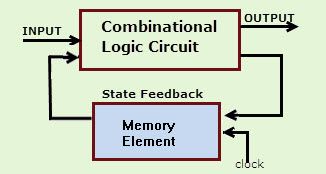

Habang mahahanap mo ang mga makabuluhang pagkakaiba-iba sa pagitan ng BJTs at JFETs, talagang maraming mga tumutugmang katangian na pag-uusapan sa mga sumusunod na talakayan. Ang pangunahing pagkakaiba sa pagitan ng mga aparatong ito ay ang BJT ay isang kasalukuyang kinokontrol na aparato tulad ng kinakatawan sa Larawan 5.1a, habang ang JFET transistor ay isang aparato na kinokontrol ng boltahe tulad ng ipinahiwatig sa Larawan 5.1b.

Sa madaling sabi, ang kasalukuyang ICsa Larawan 5.1a ay isang agarang pag-andar ng antas ng IB. Para sa FET ang kasalukuyang I ay isang pagpapaandar ng boltahe VGSna ibinigay sa input circuit tulad ng ipinakita sa Larawan 5.1b.

Sa parehong mga pagkakataon ang kasalukuyang ng output circuit ay mapamamahalaan ng isang parameter ng input circuit. Sa isang sitwasyon isang kasalukuyang antas at sa iba pang isang inilapat na boltahe.

Tulad ng npn at pnp para sa bipolar transistors, mahahanap mo ang n-channel at p-channel na mga field-effect transistor. Ngunit, dapat mong tandaan na ang BJT transistor ay isang bipolar device na awtomatikong bi- na nagpapahiwatig na ang antas ng pagpapadaloy ay isang pagpapaandar ng dalawang mga carrier ng singil, electron at butas.

Ang FET naman ay a unipolar aparato na nakasalalay lamang sa alinman sa electron (n-channel) o hole (p-channel) conduction.

Ang pariralang 'patlang na epekto' ay maaaring ipaliwanag tulad nito: lahat tayo ay may kamalayan sa lakas ng isang permanenteng pang-akit upang maakit ang mga filing ng metal patungo sa pang-akit nang walang anumang pisikal na pakikipag-ugnay. Medyo sa isang katulad na paraan sa loob ng FET isang patlang ng elektrisidad ay nilikha ng mga umiiral na singil na nakakaimpluwensya sa landas ng pagpapadaloy ng output circuit nang walang anumang direktang pakikipag-ugnay sa pagitan ng mga kontrol at dami ng kontrol. Marahil ang isa sa pinakamahalagang tampok ng FET ay ang mataas na impedance ng pag-input.

Mula sa isang lakas na 1 hanggang maraming daang megohms makabuluhang nalampasan nito ang normal na mga saklaw ng paglaban ng input ng mga pagsasaayos ng BJT, isang napakahalagang katangian habang nagkakaroon ng mga modelo ng linear ac amplifier.

Gayunpaman, ang BJT ay nagdadala ng isang higit na pagiging sensitibo sa mga pagkakaiba-iba sa input signal. Ibig sabihin, ang pagbabago sa kasalukuyang output ay karaniwang higit na malaki para sa BJT kaysa sa FET para sa parehong halaga ng pagbabago sa kanilang mga voltages ng pag-input.

Dahil dito, ang karaniwang mga nadagdag na boltahe ng ac para sa mga amplifier ng BJT ay maaaring mas mataas kaysa sa FETs.

Sa pangkalahatan, ang mga FET ay higit na mas nababanat kaysa sa BJTs, at madalas ay mas maliit ang sukat sa istraktura kumpara sa BJTs, na partikular na angkop para sa pag-embed bilang integrated-circuit (IC)chips

Ang mga katangian ng istruktura ng ilang mga FET, sa kabilang banda, ay maaaring payagan silang maging labis na sensitibo sa mga pisikal na contact kaysa sa BJTs.

Mas BJT / JFET Relasyon

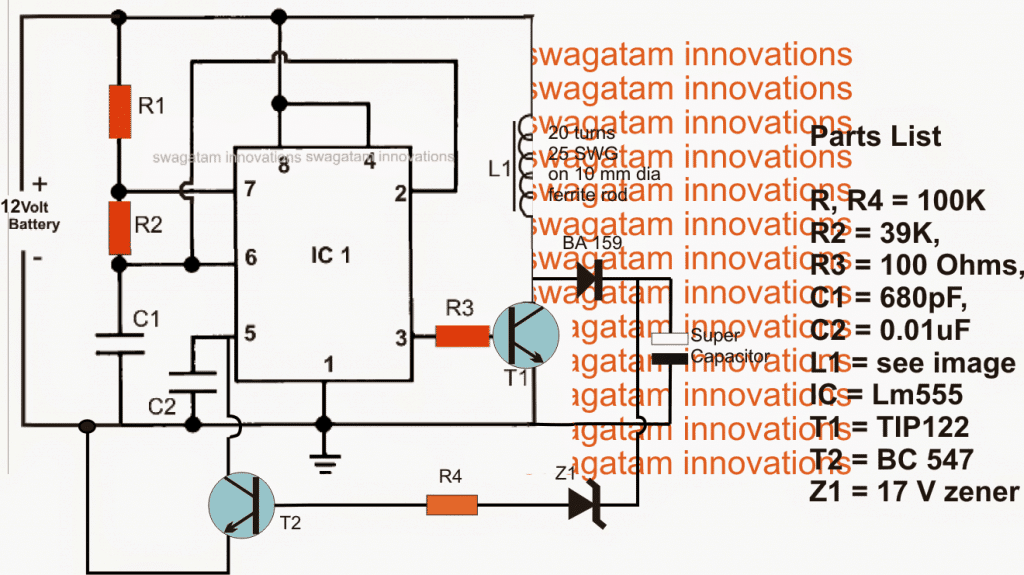

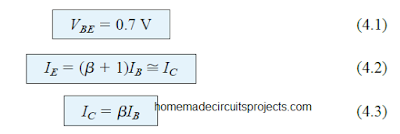

- Para sa isang BJT VMAGING= 0.7 V ang mahalagang kadahilanan para sa pagsisimula ng isang pagtatasa ng pagsasaayos nito.

- Katulad nito, ang parameter na IG= 0 Ang A ay karaniwang ang unang bagay na isinasaalang-alang para sa pagtatasa ng isang JFET circuit.

- Para sa pagsasaayos ng BJT, akoBay madalas na ang unang kadahilanan na kinakailangan upang matukoy.

- Gayundin, para sa JFET, karaniwang ito ang VGS.

Sa artikulong ito ay magtutuon kami sa JFETs o junction field effect transistors, sa susunod na artikulo ay tatalakayin namin ang tungkol sa metal-oxide-semiconductor field-effcet transistor o MOS-FET.

KONSTRUKSYON AT KATANGIAN NG JFETs

Tulad ng natutunan namin ng maaga ang isang JFET ay may 3 lead. Kinokontrol ng isa sa mga ito ang kasalukuyang daloy sa pagitan ng dalawa pa.

Tulad ng BJTs, sa JFETs din ang aparato ng n-channel ay ginagamit nang higit na prominente kaysa sa mga katapat na p-channel, dahil ang mga n aparato ay madalas na mas mahusay at madaling gamitin kumpara sa p-aparato.

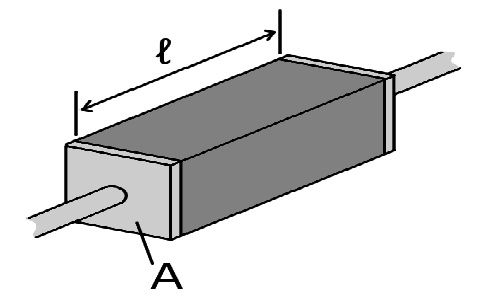

Sa sumusunod na pigura maaari nating makita ang pangunahing istraktura o pagtatayo ng isang n-channel JFET. Maaari naming makita na ang n-uri na komposisyon ay bumubuo ng punong-guro na channel sa mga layer na uri ng p.

Ang itaas na bahagi ng n-type na channel ay sumali sa pamamagitan ng isang contact na Ohmic na may termnal na pinangalanan ang alisan ng tubig (D), habang ang mas mababang seksyon ng parehong channel ay konektado din sa pamamagitan ng isang contact na Ohmic sa isa pang terminal na pinangalanang ang mapagkukunan (S).

Ang pares ng mga materyal na uri ng p ay magkakasamang naka-link sa terminal na tinukoy bilang ang gate (G). Mahalaga na nalaman namin na ang mga terminal ng alisan at pinagmulan ay sumali sa mga dulo ng n-type na channel. Ang terminal ng gate ay sumali sa isang pares ng materyal na p-channel.

Kapag walang boltahe na inilapat sa isang jfet, ang dalawang p-n junction nito ay walang anumang kundisyon sa pagkiling. Sa sitwasyong ito, may umiiral na isang rehiyon ng pag-ubos sa bawat kantong tulad ng ipinahiwatig sa itaas na pigura, na parang isang diode p-n na rehiyon na walang bias.

Water Analogy

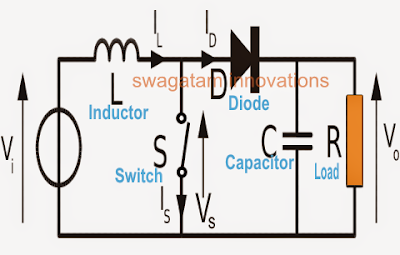

Ang mga pagpapatakbo ng pagtatrabaho at pagkontrol ng isang JFET ay maaaring maunawaan sa pamamagitan ng sumusunod na pagkakatulad ng tubig.

Dito, maihahalintulad ang presyon ng tubig sa inilapat na lakas ng boltahe mula sa alisan ng tubig patungo sa mapagkukunan.

Ang daloy ng tubig ay maihahalintulad sa daloy ng mga electron. Ginagaya ng bibig ng gripo ang pinagmulan ng terminal ng JFET, habang ang itaas na bahagi ng gripo kung saan pinipilit ang tubig ay naglalarawan sa Drain ng JFET.

Ang tap knob ay gumaganap tulad ng Gate of the JFET. Sa tulong ng isang potensyal na pag-input kinokontrol nito ang daloy ng mga electron (singil) mula sa alisan ng tubig patungo sa mapagkukunan, tulad ng pagkontrol ng tap knob sa daloy ng tubig sa pagbubukas ng bibig.

Mula sa istraktura ng JFET makikita natin na ang alisan ng tubig at ang mga pinagmulan na terminal ay nasa kabaligtaran na mga dulo ng n-channel, at dahil ang term ay batay sa daloy ng electron maaari kaming magsulat:

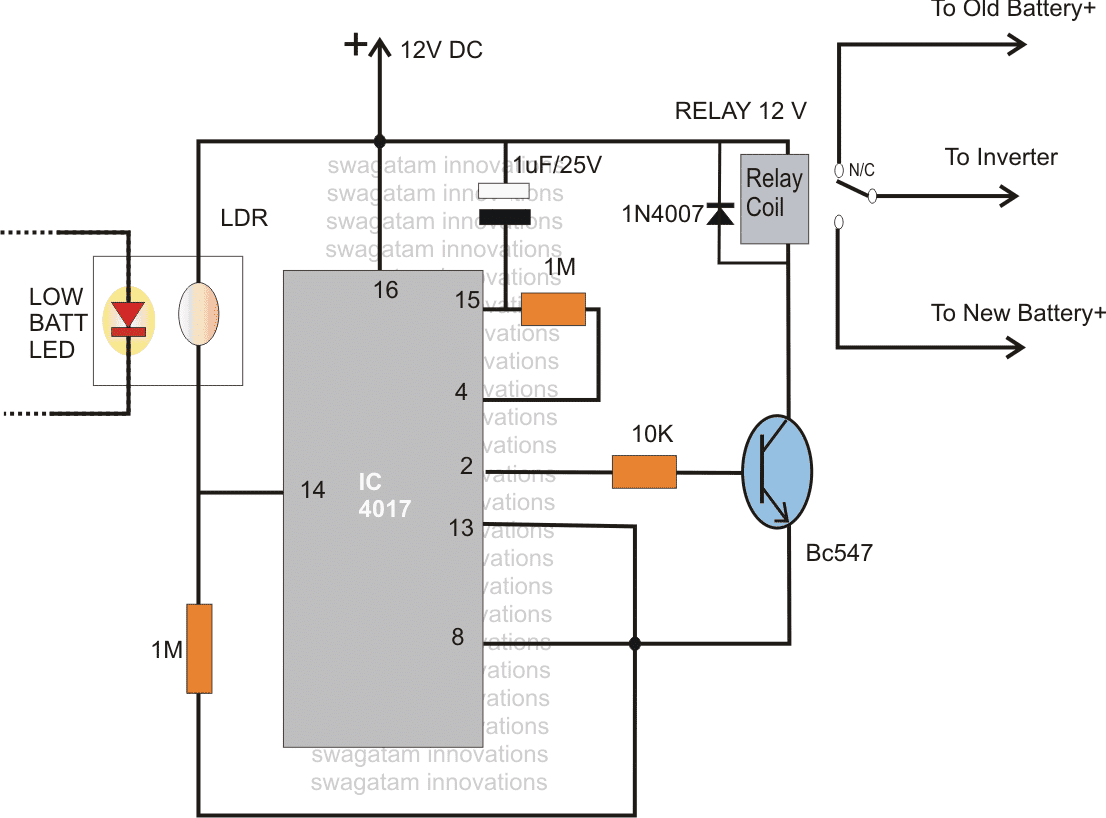

VGS= 0 V, VDSIlang Positibong Halaga

Sa Fig 5.4 maaari nating makita ang isang positibong boltahe VDSinilapat sa buong n-channel. Ang terminal ng gate ay direktang sumali sa pinagmulan upang lumikha ng isang kundisyon VGS= 0V. Pinapayagan nito ang gate at ang mga terminal ng pinagmulan na maging magkapareho ng potensyal, at nagreresulta sa isang mas mababang dulo ng rehiyon ng pag-ubos ng bawat p-materyal, eksaktong nakikita natin sa unang diagram sa itaas na may kondisyon na walang bias.

Sa lalong madaling isang boltahe VDD(= VDS) ay inilalapat, ang mga electron ay hinila patungo sa terminal ng alisan ng tubig, na bumubuo ng maginoo na daloy ng kasalukuyang ID, tulad ng ipinahiwatig sa Larawan 5.4.

Ang direksyon ng daloy ng singil ay nagpapakita na ang alisan ng tubig at kasalukuyang pinagkukunan ay pantay sa lakas (ID= AkoS). Alinsunod sa mga kundisyon na inilalarawan sa Fig 5.4, ang daloy ng singil ay mukhang hindi pinipigilan, at apektado lamang ng paglaban ng n-channel sa pagitan ng alisan ng tubig at ng mapagkukunan.

Maaari mong obserbahan na ang rehiyon ng pag-ubos ay mas malaki sa paligid ng tuktok na seksyon ng parehong mga materyal na uri ng p. Ang pagkakaiba-iba sa laki ng rehiyon ay mainam na ipinaliwanag sa pamamagitan ng Larawan 5.5. Isipin natin ang pagkakaroon ng isang pare-parehong paglaban sa n-channel, maaari itong hatiin sa mga seksyon na ipinahiwatig sa Larawan 5.5.

Ang kasalukuyang IDmaaaring buuin ang mga saklaw ng boltahe sa pamamagitan ng channel tulad ng itinuro sa parehong figure. Bilang isang resulta ang pang-itaas na rehiyon ng materyal na uri ng p ay magiging reverse bias ng isang antas ng paligid ng 1.5 V, na ang mas mababang rehiyon ay naging reverse-bias lamang ng 0.5 V.

Ang punto na ang p-n junction ay reverse-bias sa buong buong channel ay nagbibigay ng isang kasalukuyang gate na may zero amperes tulad ng ipinakita sa parehong pigura. Ang katangiang ito na humahantong sa IG= 0 Ang A ay isang mahalagang katangian ng JFET.

Bilang VDSang potensyal ay nadagdagan mula 0 hanggang sa ilang mga volts, ang kasalukuyang pagtaas ng ayon sa batas ng Ohm at ang balangkas ng IDlinya 5DSmaaaring magmukhang napatunayan sa Larawan 5.6.

Ipinapakita ng kaihambing na kawastuhan ng paglalagay na para sa mga rehiyon na mababa ang halaga ng VDS, ang paglaban ay karaniwang pare-pareho. Bilang VDStumataas at malapit sa isang antas na kilala bilang VP sa Larawan 5.6, ang mga rehiyon ng pagkaubos ay lumalawak tulad ng ibinigay sa Larawan 5.4.

Nagreresulta ito sa isang maliwanag na pagbaba ng lapad ng channel. Ang nabawasan na landas ng pagpapadaloy ay humahantong sa pagtaas ng paglaban na nagbibigay ng curve ng Larawan 5.6.

Ang mas pahalang na nakukuha ng curve, mas mataas ang paglaban, na nagpapahiwatig na ang paglaban ay papunta sa 'walang katapusang' ohms sa pahalang na rehiyon. Nang VDStataas sa isang lawak kung saan lilitaw na ang dalawang mga rehiyon ng pag-ubos ay maaaring 'makipag-ugnay' tulad ng ipinakita sa Larawan 5.7, na nagbibigay ng isang sitwasyon na kilala bilang pinch-off.

Ang halagang VDSbubuo ng sitwasyong ito ay tinawag na kurot boltahe at ito ay sinisimbolo ng VPtulad ng ipinakita sa Larawan 5.6. Sa pangkalahatan, ang salitang pinch-off ay nakaliligaw sapagkat nagpapahiwatig ito ng kasalukuyang IDay 'pinched off' at bumagsak sa 0 A. Tulad ng napatunayan sa Larawan 5.6, ito ay halos hindi maliwanag sa kasong ito. AkoDpinapanatili ang isang antas ng saturation na nailalarawan bilang IDSSsa Larawan 5.6.

Ang katotohanan ay isang napakaliit na channel na patuloy na umiiral, na may isang kasalukuyang ng makabuluhang mataas na konsentrasyon.

Ang puntong hindi mai-drop down ang ID kurot at pinapanatili ang antas ng saturation tulad ng ipinahiwatig sa Larawan 5.6 ay nakumpirma na may mga sumusunod na patunay:

Dahil walang kasalukuyang alisan ng tubig tinanggal ang posibilidad ng magkakaibang mga potensyal na antas sa pamamagitan ng materyal na n-channel para sa pagtukoy ng nagbabago na halaga ng reverse bias kasama ang p-n junction. Ang resulta ay ang pagkawala ng pamamahagi ng rehiyon na naubos na nag-trigger kurot upang magsimula sa.

Habang pinapataas natin ang VDSsa itaas ng VP, ang malapit na rehiyon ng pakikipag-ugnay kung saan ang dalawang mga rehiyon ng pag-ubos ay makakaharap ng bawat isa sa pagtaas ng haba sa kahabaan ng channel. Gayunpaman ang antas ng ID ay patuloy na mahalagang hindi nababago.

Kaya ang sandali VDSay mas mataas kaysa sa Vp, nakuha ng JFET ang mga katangian ng kasalukuyang mapagkukunan.

Tulad ng napatunayan sa Fig 5.8 kasalukuyang sa isang JFET ay natutukoy sa ID= AkoDSS, ngunit boltahe VDSmas mataas kaysa sa VP ay itinatag ng nakakonektang pagkarga.

Ang pagpili ng notasyon ng IDSS ay batay sa katotohanan na ito ay ang kasalukuyang Drain to Source na mayroong isang maikling circuited na link sa kabuuan ng gate hanggang sa mapagkukunan.

Ang karagdagang pagsisiyasat ay nagbibigay sa amin ng sumusunod na pagsusuri:

AkoDSSay ang pinakamataas na kasalukuyang alisan ng tubig para sa isang JFET at itinatag ng mga kundisyon VGS= 0 V at VDS> | VP |.

Pansinin na sa Larawan 5.6 VGSay 0V para sa kumpletong kahabaan ng curve. Sa mga sumusunod na seksyon matututunan natin kung paano ang mga katangian ng Fig 5.6 ay naiimpluwensyahan bilang antas ng VGSay iba-iba.

VGS <0V

Ang volatage na inilapat sa buong gate at pinagmulan ay sinasadya bilang VGS, na responsable para sa pagkontrol sa mga pagpapatakbo ng JFET.

Kung kukuha tayo ng halimbawa ng isang BJT, tulad din ng mga kurba ng ICvs VITOay tinutukoy para sa iba't ibang mga antas ng IB, katulad ng mga kurba ng IDvs VDSpara sa iba't ibang mga antas ng VGSmaaaring malikha para sa isang katapat na JFET.

Para sa mga ito ang terminal ng gate ay itinakda sa isang patuloy na mas mababang potensyal sa ibaba ng antas ng potensyal na mapagkukunan.

Sumangguni sa Fig.5.9 sa ibaba, isang -1V ay inilapat sa kabila ng mga terminal ng gate / pinagmulan para sa isang nabawasan na VDSantas

Ang layunin ng negatibong potensyal na bias VGSay upang paunlarin ang mga rehiyon ng pag-ubos na kahawig ng sitwasyon ng VGS= 0, ngunit sa makabuluhang nabawasan VDS.

Ito ay sanhi ng pagkamit ng gate ng isang saturation point na may mas mababang antas ng VDStulad ng ipinahiwatig sa Larawan 5.10 (VGS= -1V).

Ang katumbas na antas ng saturatio para sa IDay maaaring matagpuan mabawasan at talagang nagpapatuloy sa pagbawas ng bilang VGSginawang mas negatibo.

Malinaw mong nakikita sa Larawan 5.10 kung paano ang boltahe ng kurot-off ay nagdadala sa pag-drop na may hugis na parabolic bilang VGSlalong nagiging negatibo.

Panghuli, nang si VGS= -Vp, nakakakuha ng sapat na negatibong upang maitaguyod ang isang antas ng saturation na sa kalaunan ay 0 mA. Sa antas na ito, ang JFET ay ganap na 'naka-OFF'.

Ang antas ng VGSna sanhi koDupang maabot ang 0 mA ay nailalarawan sa pamamagitan ng VGS= VP, kung saan ang VPay isang negatibong boltahe para sa mga n-channel na aparato at isang positibong boltahe para sa mga p-channel JFET.

Karaniwan, maaari mong makita ang pagpapakita ng karamihan sa mga datasheet ng JFET kurot tinukoy ang boltahe bilang VGS (naka-off)sa halip na VP.

Ang lugar sa kanang bahagi ng pinch-off locus sa nasa itaas na pigura ay ang lugar na kinaugalian na ginagamit sa mga linear amplifier para sa pagkamit ng libreng signal ng pagbaluktot. Ang rehiyon na ito ay karaniwang tinatawag pare-pareho, kasalukuyang saturation o linear na pagpapalaki ng rehiyon.

Kinokontrol ng Boltahe na Resistor

Ang lugar na nasa kaliwang bahagi ng pinch-off locus sa parehong pigura, ay tinawag na rehiyon ng ohmic o ang rehiyon ng paglaban na kinokontrol ng boltahe.

Sa rehiyon na ito ang aparato ay maaaring sa katunayan ay pinamamahalaan bilang isang variable risistor (halimbawa sa awtomatikong makakuha ng control application), na may resistensya na kontrolado sa pamamagitan ng inilapat na potensyal / mapagkukunan ng mapagkukunan.

Maaari mong makita na ang slope ng bawat isa sa mga curve na nangangahulugan din ng alisan ng tubig / paglaban ng mapagkukunan ng JFET para sa VDS

Habang ginagawa naming mas mataas ang VGS na may negatibong potensyal, ang slope ng bawat curve ay nakakakuha ng mas pahalang, na nagpapakita ng katimbang na pagtaas ng mga antas ng paglaban.

Nakakuha kami ng isang mahusay na paunang pagtatantya sa antas ng paglaban na may paggalang sa boltahe ng VGS, sa pamamagitan ng sumusunod na equation.

Paggana ng p-Channel JFET

Ang panloob na layout at pagtatayo ng isang p-channel JFET ay tiyak na magkapareho sa katapat na n-channel, maliban na ang mga rehiyon ng materyal na p- at n-uri ay nabaligtad, tulad ng ipinakita sa ibaba:

Ang mga direksyon ng kasalukuyang daloy ay maaari ding makita bilang baligtad, kasama ang aktwal na polarities ng boltahe VGS at VDS. Sa kaso ng isang p-channel JFET, mapipigilan ang channel bilang tugon sa pagtaas ng positibong potensyal sa kabuuan ng gate / pinagmulan.

Ang notasyon na may isang dobleng subscription para sa VDSmagbibigay ng negatibong boltahe para sa VDS, tulad ng ipinakita sa mga katangian ng Fig.5.12. Dito, mahahanap mo ang IDSSsa 6 mA, habang isang boltahe ng kurot sa VGS= + 6V.

Mangyaring huwag mangalito dahil sa pagkakaroon ng minus sign para sa VDS. Ipinapahiwatig lamang nito na ang mapagkukunan ay nagdadala ng isang mas mataas na potensyal kaysa sa alisan ng tubig.

Maaari mong makita na ang mga curve para sa mataas na VDSang mga antas ay biglang tumaas sa mga halagang hindi pinipigilan. Ang ipinahiwatig na pagtaas na patayo ay sumisimbolo ng isang sitwasyon ng pagkasira, na nangangahulugang ang kasalukuyang sa pamamagitan ng aparato ng channel ay ganap na kinokontrol ng panlabas na circuitry sa puntong ito ng oras.

Bagaman hindi ito maliwanag sa Fig.5.10 para sa n-channel na aparato, maaaring ito ay isang posibilidad sa ilalim ng sapat na mataas na boltahe.

Ang rehiyon na ito ay maaaring matanggal kung ang VDS (max)ay nabanggit mula sa datasheet ng aparato, at ang aparato ay naka-configure tulad ng ang tunay na VDSang halaga ay mas mababa kaysa sa nabanggit na halagang ito para sa anumang VGS.

Nakaraan: 5 Pinakamahusay na 40 Watt Amplifier Circuits na ginalugad Susunod: 2N3055 Datasheet, Pinout, Application Circuits