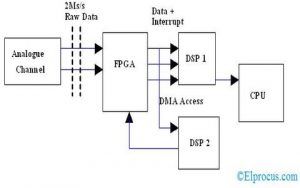

Ang terminong VLSI ay nangangahulugang 'Napakalaking Teknikal na Teknolohiya ng Pagsasama' na nagsasangkot ng pagdidisenyo ng mga integrated circuit (ICs) sa pamamagitan ng pagsasama-sama ng libu-libong transistors lohikal sa isang solong maliit na tilad sa pamamagitan ng iba't ibang mga circuit ng lohika . Ang mga IC na kalaunan ay binabawasan ang sinasakop na puwang ng circuit kung ihahambing sa mga circuit na may maginoo na IC. Ang kapangyarihan sa computational at paggamit ng puwang ang pangunahing mga hamon ng disenyo ng VLSI. Ang pagpapatupad ng mga proyekto ng VLSI ay magbubukas ng isang mapaghamong at maliwanag na karera para sa mga mag-aaral pati na rin ang mga mananaliksik. Ang ilan sa mga bagong nagte-trend na lugar ng VLSI ay Field Programmable Gate Array mga application (FPGA), mga disenyo ng ASIC, at mga SOC. Ang isang listahan ng ilan sa mga proyekto ng VLSI ay ibinibigay sa ibaba para sa mga mag-aaral na masigasig na naghahanap ng mga proyekto sa larangang ito. Tinalakay sa artikulong ito ang isang pangkalahatang ideya ng mga proyekto ng VLSI batay sa FPGA, Xilinx, IEEE, Mini, Matlab, atbp ay nakalista sa ibaba. Ang mga proyektong ito ay lubos na nakakatulong para sa mga mag-aaral sa engineering, mga mag-aaral ng M.tech.

Mga Proyekto ng VLSI para sa Mga Mag-aaral sa Engineering

Ang mga proyektong VLSI na may mga abstract para sa mga mag-aaral ng electronics engineering ay tinalakay sa ibaba.

Mga proyekto ng VLSI

1). Pagbabago ng Discrete Wavelet-based sa 3D Lifting

Nakakatulong ang proyektong ito sa pagbibigay ng lubos na tumpak na mga imahe sa pamamagitan ng paggamit ng coding ng isang imahe nang hindi nawawala ang data nito. Upang makamit ito, nagpapatupad ang prosesong ito ng isang nakakataas na filter depende sa pagbabago ng 3D discrete wavelet na arkitektura ng VLSI.

2). Pagdidisenyo ng SFQ Multiplier na may 4-bit na may Mahusay sa pamamagitan ng High-Speed Hardware

Pangunahin na ginagamit ang proyektong ito para sa pagpapatupad ng isang binagong encoder ng booth (MBE) na batay sa 4-bit SFQ nagpaparami . Ang multiplier na ito ay nagbibigay ng mahusay na pagganap kung ihahambing sa maginoo na encoder ng booth. Ang proyektong ito ay pangunahing ginagamit sa mga aplikasyon ng kritikal na pagkaantala.

3). Ginamit ang Cryptography Processor sa mga Smart Card na may Sapat na Lugar

Ginagamit ang proyektong ito upang magpatupad ng tatlong mga algorithm ng cryptography na sinusuportahan ng parehong mga pribado at pampublikong key na ginamit sa smart card mga application para sa pagbibigay ng labis na nasiguro ang pag-verify at data ng gumagamit komunikasyon .

4). Isang Mataas na Bilis o Mababang-Power Multiplier na may pamamaraang Mapang-apit na Kapangyarihan

Ang iminungkahing system na ito ay nag-filter ng walang silbi maling signal ng mga yunit ng arithmetic para sa pag-iwas sa hindi kinakailangang paghahatid ng data na hindi nakakaimpluwensya sa huling mga resulta sa computing. Gumagamit ang sistemang ito ng isang pamamaraan ng SPST para sa mga multiplier upang makamit ang mababang lakas at mabilis na paghahatid ng data.

5). Pag-compress at Decompression ng isang Lossless Data Algorithm

Pangunahing ipinatupad ang proyektong ito para sa 2-yugto na arkitektura ng hardware depende sa tampok na algorithm ng PDLZW (Parallel Dictionary LZW) pati na rin ang uri ng Adaptive Huffman na algorithm na ginagamit para sa parehong mga aplikasyon ng lossless data compression at lossless decompression.

6). Ang Arkitektura ng Turbo Decoder na may Mababang-Kakayahan para sa Energy-Efficient WSNs

Ang iminungkahing sistema ay ginagamit upang mabawasan ang kabuuang pagkonsumo ng enerhiya sa buong paghahatid ng data ng WSNs sa pamamagitan ng nabubulok na algorithm ng LUT-Log-BCJR sa pangunahing operasyon ng ACS (Add Compare Select).

7). VLSI Architecture para sa Pag-aalis ng Impulse Noise ng isang Imahe na may Episyente

Ang iminungkahing sistema na pangunahing ginagamit upang mapahusay ang kalidad ng imahe nang biswal para sa pag-iwas sa mga pagkakataong masira sa ingay ng salpok upang magpatupad ng isang mahusay na arkitekturang VLSI sa tulong ng isang napapanatili na filter.

8). Ang Arkitektura ng isang In-Memory-Processor na ginamit para sa Compression ng Multimedia

Ang iminungkahing sistema na ito ay nagbibigay ng isang mababang arkitektura para sa isang processor sa memorya upang suportahan ang mga aplikasyon ng multimedia katulad ng pag-compress ng imahe, video sa pamamagitan ng paglalapat ng napakalaking solong-tagubilin, maraming konsepto ng data at salita sa tagubilin.

9). Diskarte sa Pag-synchronize ng Timing na may isang Symbol Rate para sa mga Wireless OFDM System na may Mababang Kapangyarihan

Ang iminungkahing sistema na pangunahin na ginagamit upang mapabuti ang kilos ng wireless OFDM (Orthogonal Frequency Division Multiplexing ) system sa pamamagitan ng pagbawas ng lakas ng buong baseband sa tulong ng isang orasan generator na may phase na maaayos at pabago-bago na sample-ti-time controller.

10). Batay sa accumulator na Mababang Kapangyarihan at Mataas na Bilis na Pagpapatupad ng Multiplier na may SPST Adder & Verilog

Ang proyektong ito ay ginagamit upang magdisenyo ng isang mababang lakas at mataas na bilis ng MAC (multiplier at accumulator) sa pamamagitan ng pagtanggap ng maling pamamaraan ng pagsugpo ng kapangyarihan sa isang MBE (binago na encoder ng booth). Sa pamamagitan ng paggamit ng disenyo na ito, maiiwasan ang pagwawaldas ng kuryente ng buong paglipat.

11). Ang disenyo at pagpapatupad ng Robot Processor sa pamamagitan ng Paganahin ang Anti-banggaan sa Teknolohiya ng RFID

Ang iminungkahing sistema ay pangunahing ginagamit upang magpatupad ng isang robot processor na may anti-banggaan upang maiwasan ang pisikal na pagkakabangga ng mga robot sa kapaligiran ng multi-robot. Pangunahing ipinatutupad ang algorithm na ito gamit ang teknolohiyang VHDL & RFID.

12). Pagdidisenyo ng Logic Circuit na may Mahusay na Lakas gamit ang Adiabatic Method

Ipinapakita ng sistemang ito ang disenyo ng circuit circuit sa pamamagitan ng mahusay sa pamamaraang adiabatic kung ihinahambing sa pamamagitan ng maginoo na disenyo ng CMOS sa tulong ng mga circuit na gumagamit ng Mga pintuang NAND at NOR . Sa pamamagitan ng paggamit ng adiabatic na pamamaraan, ang pagdumi ng lakas sa loob ng network ay maaaring mabawasan pati na rin ang pag-recycle ng nakaimbak na enerhiya sa loob ng load capacitor.

3). Sistema ng Pag-encrypt para sa Pagpapahusay ng Bilis ng Computing ng System

Ang pangunahing intension ng proyektong ito ay upang mapahusay ang seguridad ng paghahatid ng data upang mapabuti ang bilis ng computing sa pamamagitan ng pagpapatupad ng algorithm ng AES gamit ang FPGA. Kaya, ang simulation na ito, pati na rin ang disenyo ng matematika, ay maaaring isagawa sa tulong ng VHDL code.

14). IP Block ng AHM o Advanced High-Performance Bus

Pangunahing ginagamit ang proyektong ito upang magdisenyo ng isang arkitektura ng Advanced Microcontroller Bus (AMB) sa pamamagitan ng paggamit ng AHBN (Advanced High-Performance Bus). Ang proyekto na ito ay maaaring idisenyo gamit ang VHDL code sa pamamagitan ng pagpapatupad ng mga bloke tulad ng master at pag-save.

15). Batay sa DSM Multimode RF Transceiver na may Multichannel

Pangunahin na ginagamit ang sistemang ito upang mag-disenyo ng isang multimode transmitter & receiver na arkitektura at RF multichannel na may Delta-Sigma modulator. Ang iminungkahing sistema na ito ay gumagamit ng isang wika ng VHDL upang magpatupad ng dalawang arkitektura.

16). Ang Concentrator ng Knockout Switch gamit ang isang Asynchronous Transfer Mode

Sa pamamagitan ng paggamit ng proyektong ito, ang isang knockout switch batay sa asynchronous transfer ay maaaring idisenyo sa tulong ng mga tool tulad ng VHS & VHDL. Ang knock out switch na ito ay maaaring magamit sa mga network ng virtual circuit packet pati na rin ang mga application ng datagram.

17). Asynchronous Circuits Pang-asal na Pagbubuo

Pangunahin na ginagamit ang proyektong ito upang maibigay ang diskarteng pag-uugali ng pag-uugali na ginamit para sa mga hindi asinkronong circuit. Parehong mga template tulad ng pagpapatupad ng balsa at asynchronous ay ang pangunahing mga elemento sa loob ng disenyo.

18). Ang Disenyo ng AMBA gamit ang Compliant Memory Controller ng AHB

Ang proyektong ito ay ginagamit upang mag-disenyo ng isang MC (memory controller) depende sa AMBA (Advanced Microcontroller Bus Architecture) para sa pagkontrol ng memorya ng system gamit ang pangunahing memorya tulad ng SRAM & ROM.

19). Pagpapatupad ng Carry Tree Adder

Ang nagdadala ng adder ng puno batay sa disenyo ng VLSI ay tinawag bilang pinakamahusay na mga pagdaragdag ng pagganap na naiiba sa pamamagitan ng karaniwang mga nagdaragdag na binary. Ang mga nagdaragdag na ipinatupad ng proyektong ito ay sumasaklaw sa puno, kogge-stone, at kalat-kalat na bato ng bato.

20). Batay sa Pag-ikot ng CORDIC Disenyo ng Fixed Angle

Ang pangunahing konsepto ng iminungkahing sistema na ito ay upang buksan ang mga vector gamit ang mga nakapirming mga anggulo. Ang mga anggulong ito ay kinakailangan para sa mga laro, robotics, pagproseso ng imahe , atbp Sa pamamagitan ng paggamit ng proyektong ito, ang pag-ikot ng vector ay maaaring makamit sa pamamagitan ng paggamit ng mga tiyak na anggulo sa pamamagitan ng disenyo ng CORDIC (coordinate rotation digital computer).

21). Unang Disenyo ng Filter na may Ipinamahaging Arithmetic ng Lookup Table

Ang iminungkahing sistema na higit sa lahat ay nagpapabuti Filter ng FIR pagganap sa pamamagitan ng pagdidisenyo nito gamit ang ipinamamahagi na arithmetic ng isang 3-dimensional na lookup na talahanayan kapalit ng multiplier. Kaya't ang disenyo na ito ay maaaring ipatupad gamit ang mga softwares tulad ng FPGA & Xilinx.

22). Push-Pull Pulsed Latches na may Mataas na Bilis at Mababang Kundisyon sa Kapangyarihan

Ang proyektong ito ay ginagamit upang magpatupad ng enerhiya-mahusay at mataas na pagganap pulsed latches pangunahin na ginagamit para sa mga sistema ng VLSI sa pamamagitan ng paggamit ng bagong topology. Dahil ang topolohiya na ito ay pangunahing nakasalalay sa isang pangwakas na yugto ng push-pull na hinihimok gamit ang dalawang mga linya ng paghati sa pamamagitan ng isang kondisyunal na generator ng pulso.

23). Arithmetic Coder VLSI Architecture sa SPIHT

Ang iminungkahing system na ito ay nagpapabuti ng throughput ng pamamaraan ng arithmetic coding sa itinakdang pagkahati sa hierarchical puno (SPIHT) na compression ng imahe na may mataas na bilis na arkitektura depende sa FPGA.

24). Pagpipigil sa Ingay ng Signal ng ECG batay sa FPGA

Ang proyektong ito ay ginagamit upang maglaman ng ingay sa loob ng mga signal ng ECG sa pamamagitan ng dalawang mga panggitna na filter na may 91 & 7 na laki ng sample point ayon sa pagkakabanggit. Kaya't ang prosesong ito ay maaaring makamit sa pamamagitan ng pagpapatupad ng Disenyo ng FPGA batay sa VHDL code.

25). Batay sa VLSI na Proseso ng Pag-scale ng Imahe na Pagganap ng Mababang Gastos

Ang proyektong ito ay ginagamit upang magpatupad ng isang algorithm para sa pag-scale ng imahe ng processor batay sa VLSI na may mas kaunting memorya at mataas na pagganap. Ang iminungkahing disenyo ng system higit sa lahat ay naglalaman ng pagsasama ng filter, reconfigurable na mga dynamic na pamamaraan at pagbabahagi ng hardware upang mabawasan ang gastos.

26). Systolic Array Architecture Disenyo at Pagpapatupad Mahusay

Ang pangunahing konsepto ng proyektong ito ay upang magdisenyo ng isang modelo ng hardware na ginamit para sa systolic array multiplier. Ang array na ito ay maaaring pangunahing magamit upang maisagawa ang binary multiplikasyon sa tulong ng VHDL platform. Ang ipinanukalang disenyo ng system ay maaaring ipatupad gamit ang FPGA & Isim software.

27). Disenyo at Pagbubuo ng QPSK gamit ang VHDL Code

QPSK ay isa sa pangunahing pamamaraan ng modulasyon. Ang pamamaraang ito ay ginagamit sa mga aplikasyon ng satellite radio. Ang pamamaraan na ito ng modulation ay maaaring ipatupad sa pamamagitan ng nababaligtad na mga gate ng lohika. Ang pagdidisenyo ng pamamaraan ng QPSK ay maaaring gawin sa tulong ng VHDL code.

28). DDR SDRAM Controller Disenyo at Pagpapatupad na may Mataas na Bilis

Ang iminungkahing sistema ay ginagamit upang mag-disenyo ng isang DDR SDRAM controller para sa paglilipat ng sumabog na data depende sa mataas na bilis upang mai-synchronize ang data na ito sa pagitan ng circuitry ng naka-embed na system at DDR SDRAM. Sa pamamagitan ng paggamit ng wikang VHDL, maaaring mabuo ang code.

29). 32 Â-bit RISC Processor Disenyo at Pagpapatupad

Ang pangunahing konsepto ng proyektong ito ay upang magpatupad ng isang 32 bit RISC (Bawas na Itinakda na Computer na Ituro) sa tulong ng isang tool tulad ng XILINK VIRTEX4. Sa proyektong ito, ang 16 na hanay ng pagtuturo ay dinisenyo saanman ang bawat tagubilin ay maaaring maipatupad sa isang solong cycle ng CLK gamit ang limang yugto na pamamaraan ng pipelining.

30). Pagpapatupad ng Bus Bridge sa pagitan ng AHB at OCP

Ang iminungkahing sistema ay ginagamit upang magdisenyo ng isang tulay ng bus sa pagitan ng dalawang mga protokol katulad ng karaniwang at pamantayan. Ang mga protocol ng komunikasyon tulad ng AHB (Advanced High-performance Bus) & OCP (Open Core Protocol) ay napakapopular na ginagamit sa mga aplikasyon ng SoC (System On-chip) .

Mga Ideya ng Proyekto ng VLSI para sa Mga Mag-aaral sa Engineering

Ang listahan ng mga proyekto ng VLSI batay sa FPGA, MatLab, IEEE, at Mini Projects para sa mga mag-aaral sa engineering ay nakalista sa ibaba.

Mga Proyekto ng VLSI para sa Mga Mag-aaral ng M. Tech

Ang listahan ng mga proyekto ng VLSI batay sa M. Tech Mga mag-aaral ay nagsasama ng sumusunod.

- Area-Efficient & Highly Reliable RHBD based I0T Memory Cell Design na ginamit sa Aerospace Applications

- Phase Detector na may Multilevel Half-Rate na ginamit para sa CLK at Mga Data Recovery Circuit

- Paghahambing na may isang Mababang Kapangyarihan at Mataas na Bilis na ginamit para sa Tiyak na Mga Aplikasyon

- Gated Voltage Level Translator na may Mataas na Pagganap at Pinagsama na Multiplexer

- Batay sa CNTFET na Ternary Adder na may Mataas na Pagganap

- Magnitude Comparator Disenyo na may Mababang Power

- Disenyo ng Threshold Logic Gate na may Kasalukuyang-Mode para sa Pag-antala ng Pagsusuri

- Disenyo ng Mixed-Logic Line Decoder na may Mababang Kapangyarihan at Mataas na Pagganap

- Disenyo ng Pagsubok sa Logic Testability ng Sleep Convention

- Boltahe na Level Shifter para sa Mga Application na Dual-Supply na may isang Mataas na Bilis at Mabilis na Pag-andar

- Mababang Power & Mababang Boltahe Dobleng-Tail Comparator Disenyo at Pagsusuri

- Disenyo ng Flip-Flop batay sa Pulse-Triggered na may Mababang-Kapangyarihan gamit ang isang Signal Feed-Through na Paraan

- Mahusay na Disenyo ng Circuits batay sa Runtime Reconfigurable FETs

- Magnitude Comparator Disenyo na may Mababang Power

- Pag-antala ng Pagsusuri ng Mga Disenyo ng Logic Gate na may Kasalukuyang-Mode Threshold

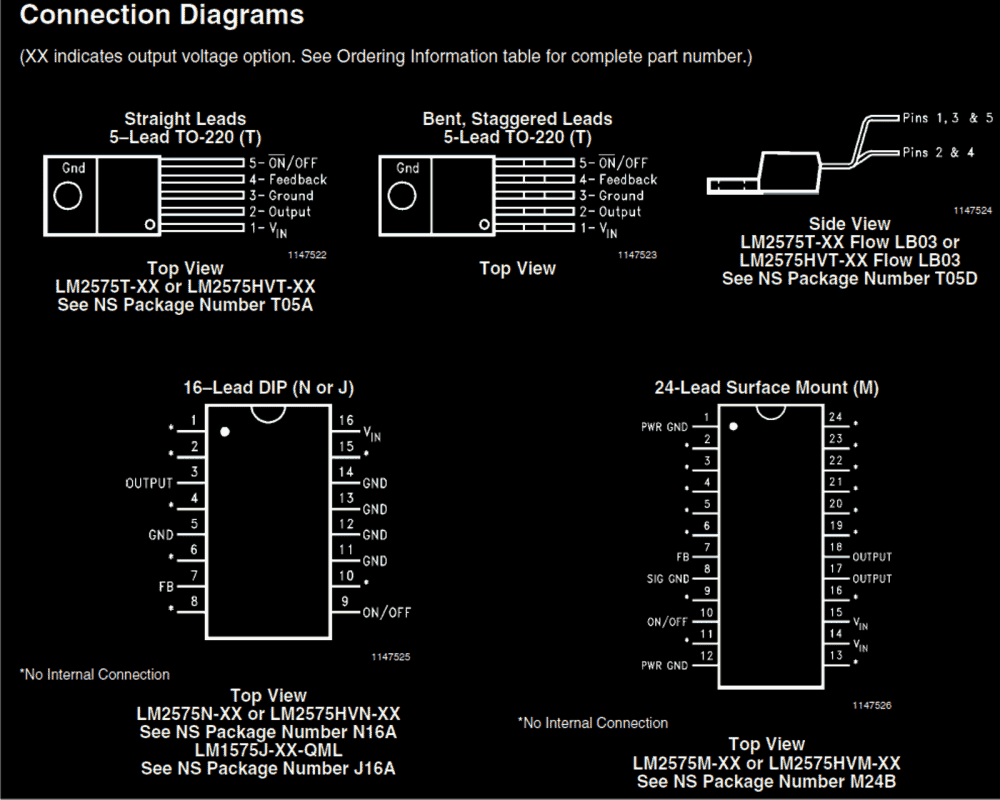

Ang Mga proyekto sa VLSI na nakabatay sa FPGA para sa mga mag-aaral sa engineering at Mga mini-proyekto ng disenyo ng CMOS VLSI ay nakalista sa ibaba.

- Ang SEU Hardened Circuits Design & Characterization para sa FPGA batay sa SRAM

- Isang Compact Memristor based CMOS hybrid LUT Disenyo at Potensyal na Aplikasyon na ginamit sa FPGA

- Batay sa Ultrasonic Sensor Pagpapatupad ng FPGA para sa Pagsukat sa Distansya

- Pagpapatupad ng FPGA para sa Booth Multiplier na may Spartan6 FPGA

- Discrete Wavelet Transform batay sa Pag-angat sa Spartan3 FPGA

- ARM Controller sa Robotics gamit ang FPGA

- Nakabatay sa FPGA ang UART kasama ang Multichannel

- Pagpigil ng ECG Signal Noise gamit ang FPGA

- Batay sa UTMI FPGA Implementation & USB 2.0 Protocol Layer

- Pagpapatupad ng Median Filter na may Spartan3 FPGA

- Batay sa AES Algorithm Pagpapatupad ng FPGA

- Security Alert System batay sa PIC para sa Pagpapatupad ng FPGA na may Spartan 3an

- Pagpapatupad ng FPGA upang Idisenyo ang Controller para sa Mga Remote Sensing System

- Image Processing Kit ng FPGA gamit ang Pag-filter ng Larawan ng Linear & Morphological

- Spartan3 FPGA batay sa Pagpapatupad ng Imaheng Medical Fusion

Ang listahan ng Mga mini proyekto ng VLSI gamit ang VHDL code kasama ang sumusunod.

- Tagapaghahambing na may Mataas na Bilis gamit ang VLSI

- Isang multiplier ng Floating-Point na gumagamit ng VLSI

- Batay sa VLSI na Conversion ng Binary to Grey

- Digital na Pagsala

- CLK Gating batay sa VLSI

- Vedic Multiplier

- Ang CMOS FF ay gumagamit ng VLSI

- Ang arkitektura ng Parallel Processor gamit ang VLSI

- Batay sa VLSI na Buong Adder

- Disenyo ng DRAM / Dynamic Random Access Memory batay sa VLSI

- Ang Layout ng SRAM batay sa VLSI

- Batay sa VLSI na Digital Signal Processor

- Batay sa VLSI na Multiplexer

- Ang pagdidisenyo ng MAC Unit batay sa VLSI

- Nakabatay sa VLSI na Pagkakaiba

- Batay sa VLSI FFT o Mabilis na Fourier Transform

- Ang arkitektura ng Discrete Cosine Transform batay sa VLSI

- 16-bit Multiplier Design gamit ang VLSI19

- Batay sa VLSI na Pagdidisenyo ng FIFO Buffer

- High-Speed Accelerator batay sa VLSI

Mga Proyekto ng VLSI na gumagamit ng MATLAB & Xilinx

Ang listahan ng mga proyekto ng VLSI batay sa MATLAB at VLSI Proyekto na gumagamit ng Xilinx ay nagsasama ng sumusunod.

- Disenyo at Pagsusuri ng Modem ng CDMA kasama ang MATLAB

- Unang Disenyo ng Filter na gumagamit ng VHDL sa Pagsusuri batay sa FPGA at MATLAB

- ModelSim & Matlab o Simulink batay sa Simulation ng System para sa Automotive Engineering

- Mga Addler na batay sa Xilinx tulad ng Ripple Carry & Carry Skip

- Ang Unit ng Arithmetic batay sa 32-bit Floating Point

- Floating Point-based ALU

- RISC Processor batay sa 32-bit

- Mga Kakayahang Convolution ng Orthogonal Code

- Xilinx at Verilog based Vending Machine

- Batay sa Xilinx na Mga Parehong Mga Pagdagdag ng Pauna na may 256-bit

- Protocol para sa Mutual Authentication gamit ang Xilinx

- Structure ng Access sa Single-Cycle para sa Logic Test gamit ang Xilinx

- UTMI at Protocol Layer batay sa USB2.0 gamit ang Xilinx

- Pag-configure ng Data Compression At Decompression gamit ang Xilinx FPGA

- Xilinx 4000 batay sa BIST at Spartan Series batay sa FPGAs

- IIR Filter batay sa MATLAB & VLSI

- FIR Filter gamit ang MATLAB

Mga Proyekto ng IEEE

Ang listahan ng IEEE VLSI Projects ay nakalista sa ibaba.

- Batay sa VLSI na Wireless Home Automation System na gumagamit ng Bluetooth

- Pag-aalis ng Impulse Noise sa loob ng Imahe sa pamamagitan ng paggamit ng isang Mahusay na Arkitektura ng VLSI

- Ang Arkitektura ng isang Processor-In-Memory para sa Multimedia Compression

- Pagsubaybay sa Sistema ng Temperatura gamit ang Cloud at IoT

- Pagpapatupad ng OFDM System na may IFFT & FFT

- Hamming Code Design & Implementation kasama ang Verilog

- Batay sa VHDL na Finger Print Recognition gamit ang Gabor Filter

- Mga Pag-andar ng Aritmetika na Pag-uulit sa ROM Depende sa Mga Malapit na Approximation

- Pagsusuri ng Mataas na Kahusayan at Mababang-Density na Pagganap ng Parity-Check Code Decoder sa Mga Application na Mababang lakas

- Mga FFT Architecture na may feedforward ng Pipelined Radix-2k

- Disenyo ng Flip-Flops para sa Mga Application ng VLSI gamit ang Teknolohiya ng CMOS na may Mataas na Pagganap

- Unang Disenyo ng Filter sa Lookup Table ng Ipinamahagi na Arithmetic

- Batay sa VLSI na Mababang Gastos at Pinahusay na Proseso ng Pag-scale ng Larawan

- Pagpapatupad at Disenyo ng ASIC ng isang Advance Turbo Encoder & Decoder na may 3GPP LTE

- Push-Pull Pulsed Latches na may Mababang Power at High-Speed Conditional

- Pinahusay na Pag-scan sa Mababang Pag-scan ng Power Power

- Arithmetic Coder VLSI Architecture para sa SPIHT

- Pagpapatupad ng VHDL para sa UART

- Batay sa Voltage Regulator ng VLSI na may Mababang Pag-drop Out

- Flash na Disenyo ng ADC na may Pinahusay na Scheme ng Paghahambing

- Mababang Power Multiplier na Disenyo na may Compound Constant Delay Logic Style

- Double Tail Comparator na may Mataas na Pagganap at Mababang lakas

- Flash Storage System na may Mataas na Pagganap depende sa Sumulat ng Buffer at Virtual Memory

- Mababang Power FF batay sa Sleepy Stack Approach

- Ang LFSR Power Optimization para sa Low-power BIST na Naipatupad sa HDL

- Disenyo at Pagpapatupad ng Machine sa Vending na may Verilog HDL

- Disenyo ng Accumulator batay sa Pagbuo ng 3-Timbang na pattern na may LP-LSFR

- Reed-Solomon Decoder na may Mataas na Bilis at Mababang-pagiging kumplikado

- Mas mabilis na diskarte sa Disenyo ng Dadda Multiplier

- Batay sa Digital Demodulation na tumatanggap ng FM Radio

- Pagbuo ng pattern ng pagsubok na may mga BIST Scheme

- Pagpapatupad ng VLSI Architecture na may High-Speed Pipeline

- On-Chip Bus OCP Protocol Design na gumagamit ng Mga Pag-andar ng Bus

- Phase Frequency Detector & Charge Pump Design na ginamit para sa High-Frequency Phase-Locked Loop

- Cache Memory & Cache Controller Design na may VHDL

- Batay sa ASTRAN Pagpapatupad ng Mababang Power 3-2 & 4-2 Adder Compressors

- Prepaid Electrical Billing System na gumagamit ng isang On-Chip Design

- Overlap na Pagpapatupad gamit ang Logic cell at Ang Pagsusuri ng Lakas nito

- Magdala Pauna sa Adder na may Iba't ibang Pagtatasa ng Pagganap ng Bit gamit ang VHDL

- Disenyo ng Layer ng Data Link sa Wi-Fi MAC Mga protokol

- Pagpapatupad ng FPGA para sa Mutual Authentication Protocol na may Modular Arithmetic

- Pagbuo ng PWM Signal na gumagamit ng FPGA at Variable Duty Cycle

Mga Proyekto ng Real-Time

Ang listahan ng Mga proyekto sa real-time na VLSI pangunahin na isama ang mga VLSI mini na proyekto gamit ang VHDL code at mga proyekto ng VLSI software para sa mga mag-aaral ng ECE engineering.

- Pragmatic Integration ng SRAM Row Cache sa Heterogeneous 3-D DRAM Architecture Gamit ang TSV

- Built-in na Diskarte sa Pagsubok sa Sarili para sa Diagnosis ng Mga pagka-antala sa Mga Pagkakasunod sa Patlang na Maaaring Programmable na Mga Cluster na Batay sa Cluster

- ASIC Disenyo ng Complex Multiplier

- Isang Pagpapatupad na Mababang Gastos ng VLSI para sa Mahusay na Pag-alis ng Ingay ng Impulse

- Batay sa FPGA Space Vector PWM Kontrolin ang IC Para sa Tatlong Phase Induction Motor Drive

- Pagpapatupad ng VLSI ng Auto Correlator at CORDIC Algorithm para sa OFDM Batay sa WLAN

- Awtomatikong pagkuha ng kalsada gamit ang mga imahe ng satellite na may mataas na resolusyon

- Disenyo ng VHDL para sa Pagse-segment ng Larawan Gamit ang Gabor Filter para sa Detection ng Sakit

- Isang Mababang pagiging kumplikado ng Turbo Decoder Architecture para sa Energy Efficient Wireless Sensor Networks

- Pagpapaganda ng Mga Kakayahang Orthogonal Code Convolution na Gamit ang Pagpapatupad ng FPGA

- Disenyo at Pagpapatupad ng Floating Point ALU

- Disenyo ng CORDIC para sa Fixed Angle of Rotation

- Mga Product Reed-Solomon Code para sa Pagpapatupad ng NAND Flash Controller sa FPGA Chip

- Basahin ang Istatistika ng SRAM na Pagpapaganda ng Pag-access sa Paggamit ng Mga Negatibong Capacitance Circuit

- Pamamahala ng Kapangyarihan ng Mga MIMO Network Interface sa Mga Mobile System

- Disenyo ng Pamantayan sa Pag-encrypt ng Data para sa Pag-encrypt ng Data

- Mababang Lakas at Mahusay na Lugar Magdala Piliin ang Adder

- Pagbubuo at Pagpapatupad ng UART Gamit ang VHDL Codes

- Pinahusay na Mga Arkitektura para sa isang Fused Floating-Point Add-Subtract Unit

- Isang FPGA Batay na 1-Bit All-Digital Transmitter na Nagtatrabaho ng Delta-Sigma Modulation na may RF Output para sa SDR

- Pag-optimize sa Paggamit ng Chain Search sa The BCH Decoder para sa Mataas na Error Rate Transmission

- Digital na Disenyo ng DS-CDMA Transmitter Gamit ang Verilog HDL at FPGA

- Disenyo at Pagpapatupad ng Mahusay na Systolic Array Architecture

- Isang Algorithm ng Pag-aaral ng Dynamics na Batay sa VLSI

- Isang Maramihang Multimedia Functional na Disenyo ng Yunit Gamit ang Malaswang Diskarte sa Pagpigil sa Lakas

- Disenyo ng Bus Bridge sa pagitan ng AHB at OCP

- Pang-asal na Pagbubuo ng mga Asynchronous Circuits

- Ang Pag-optimize ng Bilis ng isang FPGA Batay na Nabago ang Viterbi Decoder

- Pagpapatupad ng I2C Interface

- Isang High-Speed / Low-Power Multiplier Paggamit ng isang Advanced na Sprehensive Power Suppression na Diskarte

- Pag-clamping ng Virtual Supply Boltahe ng Power Gated Circuits para sa Aktibong Pagbawas ng Tagas ng Pagtulo at Pagiging maaasahan ng Gate Oxide

- FPGA Batay sa Power Efficient Channelizer para sa Software Defined Radio

- VLSI Arkitektura at FPGA Prototyping ng isang Digital Camera para sa Security ng Imahe at Pagpapatotoo

- Pagpapaunlad ng Operasyon ng Indoor Robot

- Disenyo at Pagpapatupad ng isang ON-Chip Permutation Network para sa Multiprocessor System-On-Chip

- Isang Paraan ng Symbol-Rate na Oras ng Pag-syncing ng Timing para sa Mababang Power Wireless Mga Sistemang OFDM

- DMA Controller (Direktang Pag-access sa Memorya) Paggamit ng VHDL / VLSI

- Maaaring i-configure muli ang FFT Gamit ang CORDIC Batay sa Arkitektura para sa MIMI-OFDM Mga Tatanggap

- Malaswang pamamaraan ng Pagpigil sa Kapangyarihan para sa Mga Multimedia / DSP Application

- Ang kahusayan ng BCH Codes sa Digital Image Watermarking

- Dual Data Rate SD-RAM Controller

- Pagpapatupad ng Filter ng Gabor para sa Pagkilala sa Fingerprint Gamit ang Verilog HDL

- Disenyo ng isang Praktikal na Nanometer Scale na Kalabisan sa pamamagitan ng Aware Standard Cell Library para sa Pinabuting Redundant sa pamamagitan ng 1 Insertion Rate

- Isang Lossless Data Compression at Decompression Algorithm at Ang Hardware Architecture nito

- Isang Framework para sa Pagwawasto ng Mga Multi-Bit Soft Error

- Pag-compress ng Data ng Batayang Mahusay na Batay sa Viterbi

- Pagpapatupad ng FFT / IFFT Blocks para sa OFDM

- Pagsasaayos ng Imahe na Batay sa Wavelet ng VLSI Progressive Coding

- Pagpapatupad ng VLSI ng Ganap na Pipelined Multiplier Mas Mababang 2d DCT / IDCT Architecture para sa Jpeg

- FPGA-Batay sa Fault Emulate ng Mga Kasabay na Sequential Circuits

Kaya, ito ay tungkol sa listahan ng mga proyekto ng VLSI para sa engineering, mga mag-aaral ng M.Tech na makakatulong sa pagpili ng kanilang paksang proyekto sa huling taon. Matapos gugulin ang iyong mahalagang oras habang dumadaan sa listahang ito, naniniwala kami na mayroon kang isang magandang ideya ng pagpili ng paksa ng proyekto na iyong pinili mula sa listahan ng mga proyekto ng VLSI, at inaasahan na mayroon kang sapat na kumpiyansa na kunin ang anumang paksa mula sa listahan Para sa karagdagang mga detalye at tulong sa mga proyektong ito, maaari kang sumulat sa amin sa seksyon ng mga komento na ibinigay sa ibaba. Narito ang isang katanungan para sa iyo, ano ang VHDL?

Pagkikilala sa kumuha ng larawan

- Mga proyekto ng VLSI ni set-tech