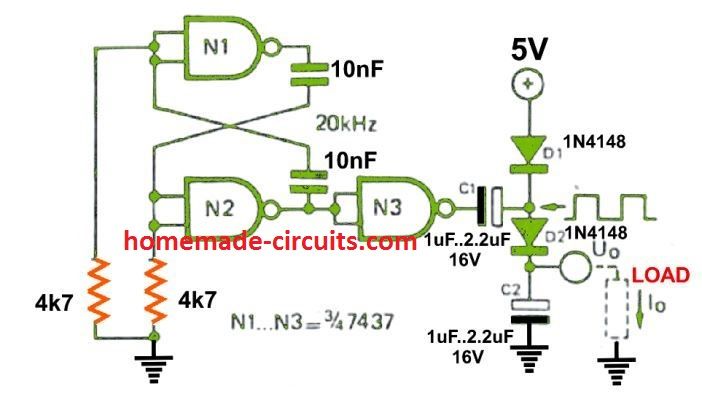

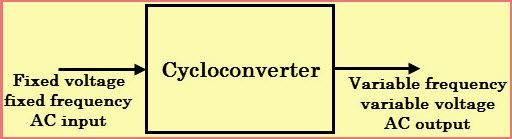

Ang MOS transistor ay ang pinakapangunahing elemento sa malakihang integrated circuit na disenyo. Ang mga transistor na ito ay karaniwang inuri sa dalawang uri ng PMOS at NMOS. Ang kumbinasyon ng NMOS at PMOS transistors ay kilala bilang a CMOS transistor . Ang iba mga pintuan ng lohika at iba pang digital logic device na ipinapatupad ay dapat may PMOS logic. Ang teknolohiyang ito ay mura at may mahusay na panlaban sa panghihimasok. Tinatalakay ng artikulong ito ang isa sa mga uri ng MOS transistor tulad ng isang PMOS transistor.

Ano ang PMOS Transistor?

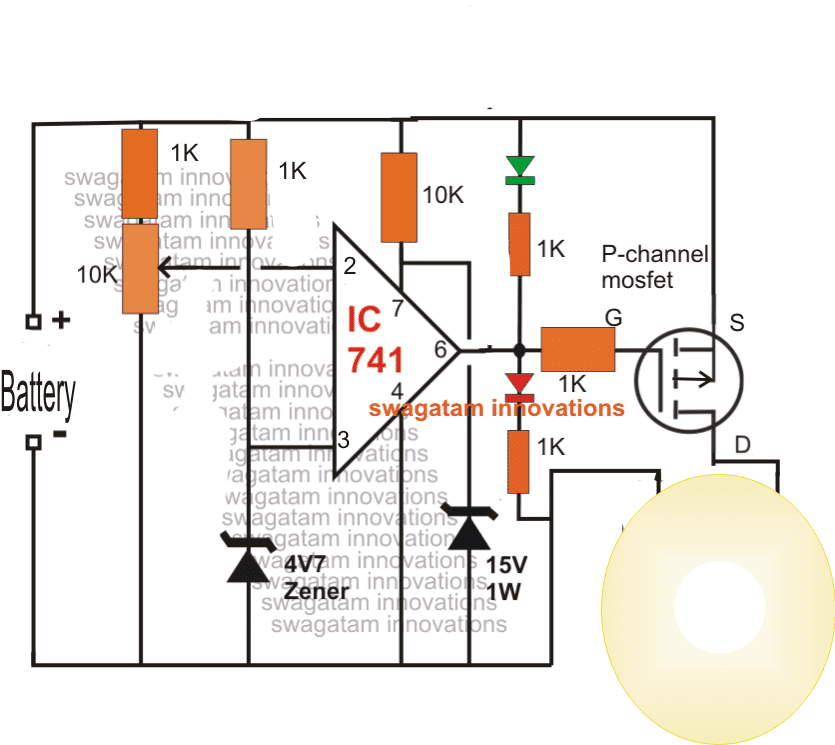

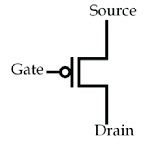

Ang PMOS transistor o P-channel metal oxide semiconductor ay isang uri ng transistor kung saan ang mga p-type na dopant ay ginagamit sa channel o rehiyon ng gate. Ang transistor na ito ay eksaktong kabaligtaran ng NMOS Transistor. Ang mga transistor na ito ay may tatlong pangunahing terminal; ang pinagmulan, ang gate at ang drain kung saan ang pinagmulan ng transistor ay idinisenyo gamit ang isang p-type na substrate, at ang drain terminal ay dinisenyo na may isang n-type na substrate. Sa transistor na ito, ang mga carrier ng singil tulad ng mga butas ay responsable para sa pagpapadaloy ng kasalukuyang. Ang mga simbolo ng transistor ng PMOS ay ipinapakita sa ibaba.

Paano Gumagana ang PMOS Transistor?

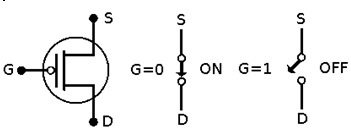

Ang p-type na transistor na gumagana ay medyo kabaligtaran sa n-type na transistor. Ang transistor na ito ay bubuo ng isang bukas na circuit sa tuwing ito ay nakakakuha ng non-negligible na boltahe na nangangahulugang, walang daloy ng kuryente mula sa gate (G) terminal patungo sa source (S). Katulad nito, ang transistor na ito ay bumubuo ng closed circuit kapag nakakuha ito ng boltahe sa humigit-kumulang 0 volts na nangangahulugang ang kasalukuyang dumadaloy mula sa gate (G) terminal patungo sa drain (D).

Ang bubble na ito ay kilala rin bilang isang inversion bubble. Kaya ang pangunahing pag-andar ng bilog na ito ay upang baligtarin ang halaga ng boltahe ng input. Kung ang gate terminal ay nagbibigay ng 1 boltahe, ang inverter na ito ay babaguhin ito sa zero at gumagana ang circuit nang naaayon. Kaya ang pag-andar ng PMOS transistor at NMOS transistor ay medyo kabaligtaran. Kapag pinagsama namin ang mga ito sa isang solong MOS circuit, ito ay magiging isang CMOS (complementary metal-oxide semiconductor) circuit.

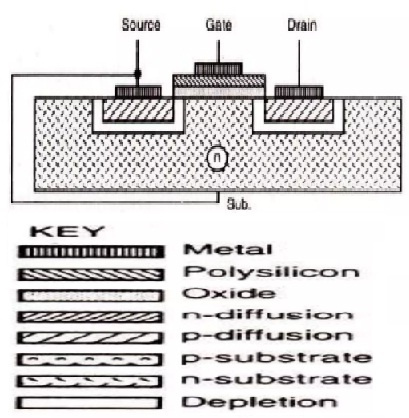

Cross Section ng PMOS Transistor

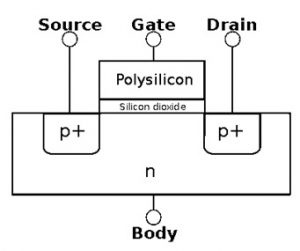

Ang cross-section ng PMOS transistor ay ipinapakita sa ibaba. Ang isang pMOS transistor ay binuo gamit ang isang n-type na katawan kabilang ang dalawang p-type na mga rehiyon ng semiconductor na katabi ng gate. Ang transistor na ito ay may controlling gate tulad ng ipinapakita sa diagram na kumokontrol sa daloy ng mga electron sa pagitan ng dalawang terminal tulad ng source at drain. Sa pMOS transistor, ang katawan ay gaganapin sa +ve boltahe. Kapag positibo na ang gate terminal, reverse-biased ang source at drain terminal. Kapag nangyari ito, walang daloy ng kasalukuyang, kaya ang transistor ay i-OFF.

Kapag ang supply ng boltahe sa terminal ng gate ay ibinaba, pagkatapos ay maaakit ang mga carrier ng positibong charge sa ilalim ng interface ng Si-SiO2. Sa tuwing ang boltahe ay bumaba nang sapat, ang channel ay mababaligtad at lilikha ng isang conducting pathway mula sa source terminal patungo sa drain sa pamamagitan ng pagpayag sa daloy ng kasalukuyang.

Sa tuwing ang mga transistor na ito ay nakikitungo sa digital na lohika, karaniwang mayroong dalawang magkaibang mga halaga tulad lamang ng 1 & 0 (ON at OFF). Ang positibong boltahe ng transistor ay kilala bilang VDD na kumakatawan sa logic na mataas (1) na halaga sa loob ng mga digital circuit. Ang mga antas ng boltahe ng VDD sa TTL logic sa pangkalahatan ay nasa paligid ng 5V. Sa kasalukuyan, ang mga transistor ay hindi maaaring aktwal na makatiis ng mga ganoong kataas na boltahe dahil ang mga ito ay karaniwang mula sa 1.5V - 3.3V. Ang mababang boltahe ay madalas na kilala bilang GND o VSS. Kaya, ang VSS ay nagpapahiwatig ng logic na '0' at ito ay nakatakda din nang normal sa 0V.

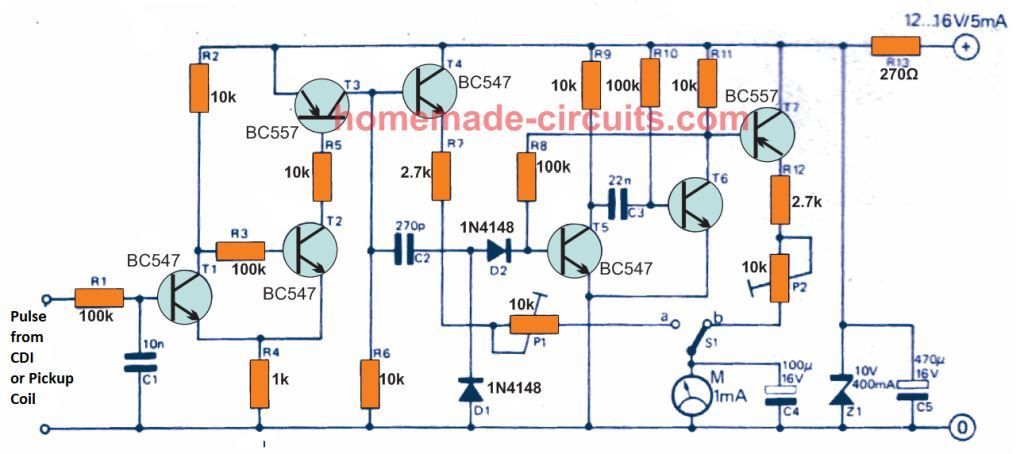

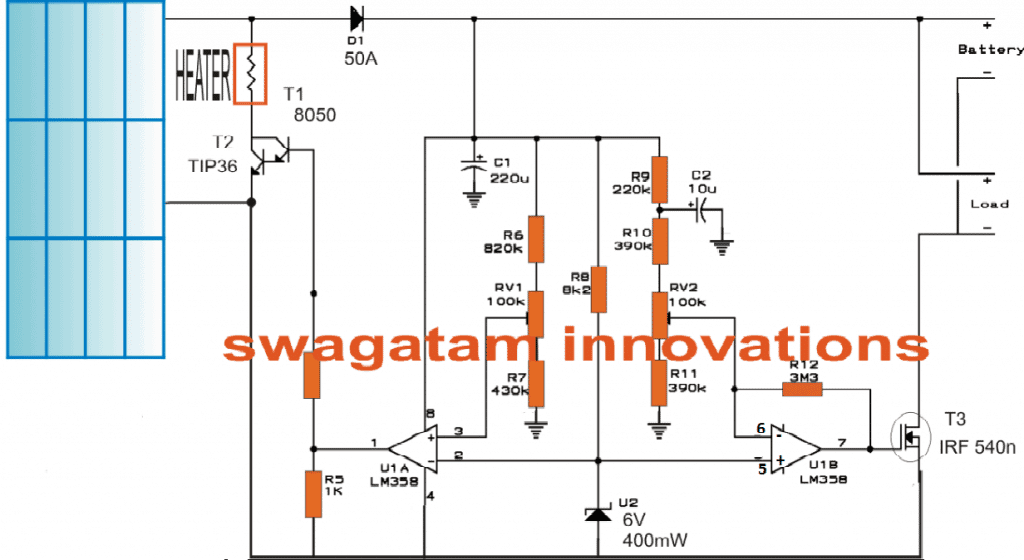

PMOS Transistor Circuit

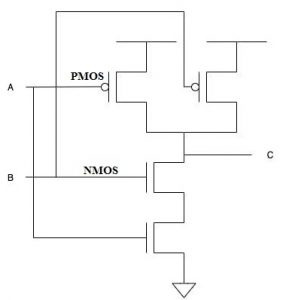

Ang disenyo ng NAND gate gamit ang PMOS transistor at NMOS transistor ay ipinapakita sa ibaba. Sa pangkalahatan, ang NAND gate sa digital electronics ay isang logic gate na tinatawag ding NOT-AND gate. Ang output ng gate na ito ay mababa (0) lamang kung ang dalawang input ay mataas (1) at ang output nito ay isang pandagdag sa isang AND gate. Kung ang alinman sa dalawang input ay LOW (0), kung gayon ito ay nagbibigay ng mataas na resulta ng output.

Sa ibaba ng logic circuit, kung ang input A ay 0 at B ay 0, ang isang input ng pMOS ay gagawa ng '1' at ang isang input ng nMOS ay gagawa ng '0'. Kaya, ang logic gate na ito ay bumubuo ng isang lohikal na '1' dahil ito ay konektado sa pinagmulan sa pamamagitan ng isang closed circuit at hiwalay mula sa GND sa pamamagitan ng isang bukas na circuit.

Kapag ang A ay '0' at B' ay '1', ang isang input ng pMOS ay bubuo ng isang '1' at Ang isang input ng NMOS ay bubuo ng isang '0'. Kaya, ang gate na ito ay gagawa ng isang lohikal dahil ito ay konektado sa pinagmulan sa pamamagitan ng isang closed circuit at hiwalay mula sa GND sa pamamagitan ng isang bukas na circuit. Kapag ang A ay '1' at ang B ay '0', kung gayon ang 'B' na input ng pMOS ay bubuo ng mataas na output (1) at 'B' na input ng NMOS ay bubuo ng isang output bilang mababang (0). Kaya, ang logic gate na ito ay bubuo ng isang lohikal na 1 dahil ito ay konektado sa pinagmulan sa pamamagitan ng isang closed circuit at hiwalay sa GND ng isang bukas na circuit.

Kapag ang A ay '1' at ang B ay '1', ang isang input ng' pMOS ay gagawa ng zero, at ang isang input ng nMOS ay bubuo ng '1'. Dahil dito, dapat nating i-verify ang B input ng pMOS at nMOS din. Ang B input ng pMOS ay bubuo ng isang '0' at B input ng nMOS ay bubuo ng isang '1'. Kaya, ang logic gate na ito ay bubuo ng isang lohikal na '0' dahil ito ay nahiwalay sa pinagmulan ng isang bukas na circuit at nakakonekta sa GND sa pamamagitan ng isang closed circuit.

Talahanayan ng Katotohanan

Ang talahanayan ng katotohanan ng logic circuit sa itaas ay ibinigay sa ibaba.

|

A |

B |

C |

|

0 |

0 | 1 |

|

0 |

1 | 1 |

| 1 | 0 |

1 |

| 1 | 1 |

0 |

Ang threshold na boltahe ng PMOS Transistor ay karaniwang ang 'Vgs' na kinakailangan upang lumikha ng channel na kilala bilang channel inversion. Sa isang PMOS transistor, ang substrate at ang source terminal ay konektado lang sa 'Vdd'. Kung sisimulan nating bawasan ang boltahe sa pamamagitan ng pagtukoy sa source terminal sa gate terminal mula Vdd hanggang sa isang punto kung saan mo man mapansin ang pagbaligtad ng channel, sa posisyong ito kung susuriin mo ang Vgs at source na nasa mataas na potensyal, makakakuha ka ng negatibong halaga. Kaya, ang PMOS transistor ay may negatibong Vth value.

Proseso ng Paggawa ng PMOS

Ang mga hakbang na kasangkot sa PMOS transistor fabrication ay tinalakay sa ibaba.

Hakbang 1:

Ang isang manipis na silicon wafer layer ay binago sa N-type na materyal sa pamamagitan lamang ng doping phosphorous na materyal.

Hakbang 2:

Ang isang makapal na Silicon dioxide (Sio2) na layer ay lumago sa isang kumpletong p-type na substrate.

Hakbang 3:

Ngayon ang ibabaw ay pinahiran ng isang photoresist sa ibabaw ng makapal na layer ng silikon dioxide.

Hakbang 4:

Pagkatapos nito, ang layer na ito ay nakalantad lamang sa UV light sa pamamagitan ng isang maskara na tumutukoy sa mga rehiyon kung saan ang pagsasabog ay magaganap kasama ng mga transistor channel.

Hakbang 5:

Ang mga rehiyong ito ay nakaukit nang magkapareho sa pinagbabatayan ng silicon dioxide upang ang ibabaw ng ostiya ay nakalantad sa loob ng bintana na tinukoy ng maskara.

Hakbang 6:

Ang natitirang photoresist ay hiwalay at ang manipis na Sio2 layer ay karaniwang lumalaki sa 0.1 micrometer sa buong ibabaw ng chip. Pagkatapos nito, ang polysilicon ay inilalagay sa ibabaw nito upang mabuo ang istraktura ng gate. Ang isang photoresist ay inilalagay sa ibabaw ng buong polysilicon layer at inilalantad ang UV light sa pamamagitan ng mask2.

Hakbang 7:

Nakakamit ang mga diffusion sa pamamagitan ng pag-init ng wafer hanggang sa pinakamataas na temperatura at pagpasa ng gas na may mga gustong p-type na impurities tulad ng Boron.

Hakbang 8:

Ang isang 1-micrometer na kapal ng silicon dioxide ay lumaki at ang photoresist na materyal ay idineposito dito. Ilantad ang ultraviolet light na may mask3 sa mga gustong lugar ng gate, source at drain na nakaukit para maputol ang contact.

Hakbang 9:

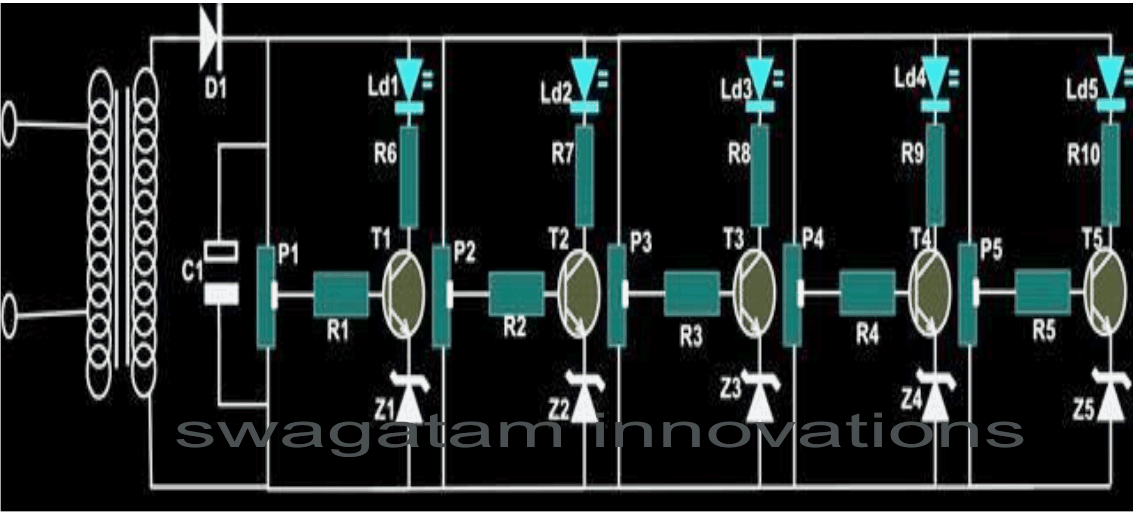

Ngayon isang metal o aluminyo ang idineposito sa ibabaw ng 1-micrometer na kapal nito. Muli, isang photoresist na materyal ang pinatubo sa buong metal at inilantad ang UV light sa pamamagitan ng mask4 na nakaukit upang bumuo ng kinakailangang interconnection na disenyo. Ang huling istraktura ng PMOS ay ipinapakita sa ibaba.

Mga Katangian ng PMOS Transistor

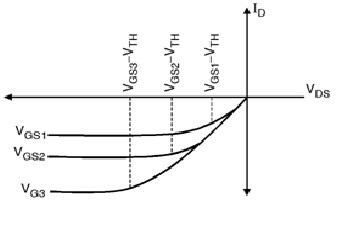

Ang mga katangian ng PMOS transistor I-V ay ipinapakita sa ibaba. Ang mga katangiang ito ay nahahati sa dalawang rehiyon upang makuha ang ugnayan sa pagitan ng drain sa source current (I DS) pati na rin ang mga terminal voltage nito tulad ng mga linear at saturation na rehiyon.

Sa isang liner na rehiyon, ang IDS ay linearly tataas kapag ang VDS (drain to source voltage) ay tumaas samantalang sa saturation region, ang I DS ay stable at ito ay independiyente sa VDS. Ang pangunahing ugnayan sa pagitan ng ISD (pinagmulan upang maubos ang kasalukuyang) at ang mga boltahe ng terminal nito ay nakuha ng isang katulad na pamamaraan ng NMOS transistor. Sa kasong ito, ang tanging pagbabago ay ang mga carrier ng singil na nasa loob ng inversion layer ay mga butas lamang. Kapag ang mga butas ay lumipat mula sa pinagmulan patungo sa alisan ng tubig, ang daloy ng kasalukuyang ay pareho din.

Kaya, ang negatibong palatandaan ay lilitaw sa loob ng kasalukuyang equation. Bilang karagdagan, ang lahat ng inilapat na bias sa mga terminal ng device ay negatibo. Kaya, ang PMOS transistor's ID - mga katangian ng VDS ay ipinapakita sa ibaba.

Ang drain current equation para sa PMOS transistor sa linear na rehiyon ay ibinibigay bilang:

ID = – mp Cox

Gayundin, ang Drain current equation para sa PMOS transistor sa saturation region ay ibinibigay bilang:

ID = – mp Cox (VSG – | V TH |p )^2

Kung saan ang 'mp' ay ang mobility ng butas at '|VTH| p’ ay ang threshold voltage ng PMOS transistor.

Sa equation sa itaas, ang negatibong sign ay magsasaad na ang ID( alisan ng tubig ang kasalukuyang ) ay dumadaloy mula sa alisan ng tubig (D) patungo sa pinagmulan (S) samantalang ang mga butas ay dumadaloy sa kabaligtaran na direksyon. Kapag ang mobility ng butas ay mababa kumpara sa electron mobility, ang PMOS transistors ay nagdurusa sa kakayahan ng low current drive.

Kaya, ito ay tungkol sa isang pangkalahatang-ideya ng PMOS transistor o p-type na mos transistor - katha, circuit, at gumagana nito. PMOS ang mga transistor ay dinisenyo na may p-source, n-substrate at drain. Ang mga tagadala ng singil ng PMOS ay mga butas. Ang transistor na ito ay nagsasagawa sa sandaling inilapat ang mababang boltahe sa terminal ng gate. Ang mga aparatong nakabatay sa PMOS ay hindi gaanong madaling makagambala kumpara sa mga aparatong NMOS. Ang mga transistor na ito ay maaaring gamitin bilang mga resistor na kinokontrol ng boltahe, aktibong pagkarga, kasalukuyang salamin, trans-impedance amplifier, at ginagamit din sa mga switch at amplifier ng boltahe. Narito ang isang tanong para sa iyo, ano ang isang NMOS transistor?