Gamit ang isang hanay ng mga latch / reset na network naging posible upang payagan ang isang lohika na lumipat sa isang pasulong na pagkakasunud-sunod, lumilipat SA isang naibigay na hanay ng mga output TAAS, bilang tugon sa isang alternating input na orasan. At kapag naabot na ang maximum na limitasyon, ang mga input na orasan ay nagsisimulang magsara o mag-alis ng pagkakasunud-sunod sa kabaligtaran na pagkakasunud-sunod.

Kaya, ang pagkakasunud-sunod ng pababa ay kinokontrol sa pamamagitan ng isang solong pag-oscillating signal ng input ng orasan.

Maaari ding ipaliwanag ang proseso tulad ng sumusunod:

Bilang tugon sa isang inilapat na orasan ng paglipat ang circuit ay nagsisimula sa pagdaragdag ng HIGH logics sa mga output sa isang pagtaas ng pagkakasunud-sunod at sa sandaling maabot ang maximum na limitasyon, nagsisimula itong ibawas ang TAAS mula sa output sa pamamagitan ng pag-render sa kanila ng LOW sa kabaligtaran na pagkakasunud-sunod, bilang tugon sa inilapat signal ng orasan.

Narito lamang ang 4 na output ay ipinapakita mula noong Ang IC 4043 ay mayroon lamang 4 na pares ng mga set / reset latches , gayunpaman ang bilang ay maaaring posibleng tumaas sa pamamagitan ng pag-cascading ng IC 4017 at sa pamamagitan ng pagdaragdag ng isa pang 4043 IC sa mayroon nang isa. Papayagan kaming makakuha ng 8 mga numero ng pagkakasunud-sunod ng set / reset o 8 pares ng mga pataas / pababang output.

Paglalapat

Ang circuit na ito ay maaaring maging napaka kapaki-pakinabang para sa pagkontrol ng isang naibigay na parameter na tulad ng anumang karagdagang pagtaas ng parameter ay na-inhibit sa lalong madaling lumampas ang maximum na limitasyon, at sa kabaligtaran ang proseso ay naibalik at pinasimulan kapag ang limitasyon ay bumalik sa loob ng saklaw.

Halimbawa maaari itong mailapat sa maliliit na elevator upang payagan lamang ang 3 tao na makapasok sa loob ng pag-angat, sa sandaling lumampas ang limitasyong ito, ang elevator ay na-inhibit mula sa pagsisimula, ngunit sa sandaling maibalik ang limitasyon ay pinapayagan ang paglipat ng elevator.

Paano gagana ang UP / Down sequencer na ito

Ang circuit na ito ay orihinal na nilikha upang simulan ang mga power supply nang sunud-sunod at pagkatapos ay patayin ang mga ito sa pangalawang pagkakataon sa kabaligtaran na pagkakasunud-sunod. Ang tampok na ito ay maaaring maging madalas na kapaki-pakinabang para sa tinkering gamit ang mga kagamitan at circuit kung saan kailangang gamitin ang kuryente at ilabas sa isang tukoy na pagkakasunud-sunod.

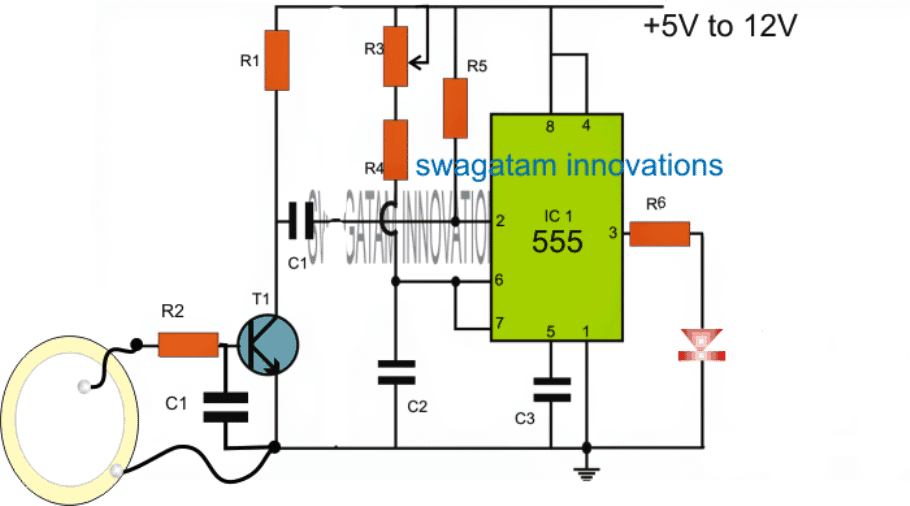

Ang pangunahing seksyon ng circuit ay ang counter ng kabayo ng IC 4017 CMOS dekada counter. Ang mga output na Q1 hanggang Q4 ay nasanay na magtaguyod ng mga latches nang serial sa pagkakasunud-sunod ng 1-2-3-4, pagkatapos nito ay tumigil na ang pagbibilang. Ang pagpindot sa switch S1 ay nagbibigay-daan sa pagbibilang upang magpatuloy, at ngayon ang counter output Q5 hanggang Q8 ay inilalapat upang i-reset ang mga latches sa kabaligtaran na pagkakasunud-sunod, ibig sabihin sa pagkakasunud-sunod 4-3-2-1. Ang huling output, Q9, ay ginagamit upang ihinto ang counter.

Sa sandaling ang kapangyarihan ay nakabukas SA, C2 at R2 sa unang render ang counter sa posisyon ng pag-reset. Kapag naging matatag ang boltahe ng suplay ng kuryente, ang signal ng pag-reset ay tuluyang bumababa na pinapayagan ang 4017 upang simulan ang pagbibilang sa signal ng orasan na 1-Hz na nakuha sa pamamagitan ng isang osiloster na binubuo ng IC1d, R3 at C3.

Ang mga output pin ng IC 4017 ay napalitaw nang sunud-sunod sa bawat tumataas na gilid ng pulso ng orasan. Gayunpaman habang dumating ang sumusunod na pulso ng orasan ang huling output ay nakasara.

Ang mga latches sa quad RS-latch type 4043 ay ginagawang posible para sa mga output na manatiling aktibo. Humihinto ang IC2 sa pagbibilang sa Q4 dahil sa IC1b na inaalis ang signal na paganahin ang orasan sa pin 13 sa pamamagitan ng IC1a.

Upang mapahintulutan ang 4017 na magpatuloy sa pagbibilang at samakatuwid patayin ang mga output, kailangang pindutin ang S1, na muling paganahin ang orasan na paganahin sa pin 13.

Ang mga counter output Q5 hanggang Q8 ay nakakabit sa mga reset ng pag-reset ng mga latches, sa gayon habang gumagalaw ang pagkakasunud-sunod ng IC2, ang mga latches ay nai-reset sa pabalik na direksyon. Ang proseso ng pagbibilang ay sa kalaunan ay tumigil sa Q9 ng IC lc, na muling tinatanggal ang signal na nagpapagana ng orasan.

Mataas na halaga, mababang kasalukuyang mga pull-up resistor (R4-R7) ay ginagamit sa mga input ng latch na 'reset' upang maiwasang hindi masimulan ang mga sitwasyon.

Listahan ng Mga Bahagi

Mga resistorista (Lahat ng resistors ay 1/4 wat 5%)

R1 = 4K7

R3 = 4M7

R2, R4, R5, R6, R7 = 1M

Mga capacitor

C1, C4, C5 = 0.1uF / ceramic

C2 = 22uF / 25V

C3 = 1uF / 25V

Pinagsamang Circuits

IC 4017 = 1no

IC 4043 = 1no

IC 4093 = 1hindi

S1 = itulak sa ON switch

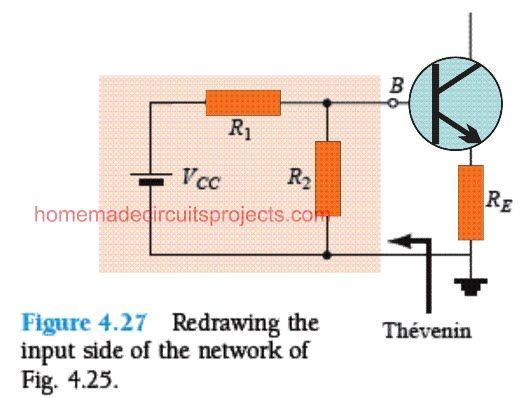

Nakaraan: Button ng Motorsiklo Magsimula sa Pag-lock ng Circuit Susunod: DC Biasing sa Transistors - BJTs