Dalawang pangunahing uri ng FET na kasalukuyang umiiral ay: JFETs at MOSFETs.

Ang MOSFETs ay maaaring karagdagang naiuri sa uri ng pag-ubos at uri ng pagpapahusay. Ang parehong mga uri ay tumutukoy sa pangunahing mode ng pagpapatakbo ng MOSFETs, habang ang katagang MOSFET mismo ay ang pagpapaikli ng metal-oxide-semiconductor-field-effect transistor.

Dahil sa ang katunayan na ang dalawang uri ay may magkakaibang mga katangian sa pagtatrabaho, susuriin namin ang bawat isa sa kanila nang magkahiwalay sa iba't ibang mga artikulo.

Pagkakaiba sa pagitan ng Pagpapahusay at Pag-ubos ng MOSFET

Talaga, hindi katulad ng mga pagpapahusay na MOSFET, ang pag-ubos ng MOSFETs ay nasa isang on-state kahit na may pagkakaroon ng 0 V sa kabila ng mga gate-to-source terminal (VGS).

Para sa isang pagpapahusay na MOSFET, ang gate-to-source voltage (VGS) ay dapat na nasa itaas ng kanyang gate-to-source threshold voltage (VGS (th)) upang maisagawa ito .

Gayunpaman, para sa isang pag-ubos ng N-channel na MOSFET, ang halaga ng VGS (ika) nito ay higit sa 0 V. Nangangahulugan ito na kahit na VGS = 0 V, ang isang pag-ubos ng MOSFET ay maaaring magsagawa ng kasalukuyang. Upang i-off ito, ang VGS ng isang pag-ubos ng MOSFET ay kailangang mabawasan sa ibaba ng VGS (ika) (negatibo).

Sa kasalukuyang artikulong ito tatalakayin natin ang pagkaubos na uri ng MOSFET, na sinasabing mayroong mga katangian na tumutugma sa isang JFET. Ang pagkakapareho ay sa pagitan ng cut-off at saturation na malapit sa IDSS.

Pangunahing Konstruksyon

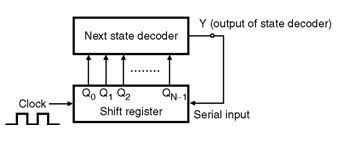

Ipinapakita ng Fig.5.23 ang pangunahing panloob na istraktura ng isang n-channel depletion-type MOSFET.

Maaari kaming makahanap ng isang bloke ng p-type na materyal na nilikha gamit ang isang silicon base. Ang block na ito ay tinatawag na substrate.

Ang substrate ay ang base o ang pundasyon kung saan itinayo ang isang MOSFET. Para sa ilang MOSFET na panloob na naka-link sa terminal na 'pinagmulan'. Gayundin, maraming mga aparato ang nag-aalok ng isang labis na output sa anyo ng SS, na nagtatampok ng isang 4-terminal MOSFET, tulad ng isiniwalat sa Fig.5.23

Ang alisan ng tubig at ang mga pinagmulan na terminal ay konektado sa pamamagitan ng mga kondaktibong contact sa mga n-doped na lokasyon, at nakalakip sa pamamagitan ng isang n-channel, tulad ng ipinahiwatig sa parehong pigura.

Ang gate ay konektado din sa isang metallic layer, kahit na ito ay insulated mula sa n-channel sa pamamagitan ng isang pinong layer ng silicon dioxide (SiOdalawa).

SiOdalawanagtataglay ng isang natatanging anyo ng pag-aari ng pagkakabukod na tinatawag na dielectric na lumilikha ng isang salungat na larangan ng kuryente sa loob mismo bilang tugon sa isang panlabas na larangang elektrikal.

Ang pagiging isang insulate layer, ang materyal na SiOdalawaInaalok sa amin ang sumusunod na mahalagang impormasyon:

Ang isang kumpletong paghihiwalay ay binuo sa pagitan ng terminal ng gate at ang mosfet channel sa materyal na ito.

Bukod dito, ito ay dahil sa SiOdalawa, ang gate ng mosfet ay maaaring magtampok ng isang napakataas na antas ng input impedance.

Dahil sa napakahalagang mataas na pag-aari ng impedance na ito, ang kasalukuyang gate ng IGay halos zero amps para sa anumang dc-bias na pagsasaayos ng MOSFET.

Pangunahing Pagpapatakbo at Mga Katangian

Tulad ng makikita sa Fig.5.24, ang gate sa pinagmulan ng boltahe ay na-configure sa zero volts sa pamamagitan ng pagkonekta ng dalawang mga terminal nang magkasama, habang isang boltahe VDSay inilapat sa buong mga terminal ng alisan at pinagmulan.

Sa setting sa itaas, ang gilid ng alisan ng tubig ay nagtatatag ng isang positibong potensyal ng mga n-channel na libreng electron, kasama ang isang katumbas na kasalukuyang sa pamamagitan ng JFET channel. Gayundin, ang nagresultang kasalukuyang VGS= 0V ay kinikilala pa rin bilang IDSS, tulad ng ibinigay sa Larawan 5.25

Maaari nating makita iyon sa Fig.5.26 ang boltahe ng mapagkukunan ng gate VGSay binibigyan ng isang negatibong potensyal sa anyo ng -1V.

Sinusubukan ng negatibong potensyal na pilitin ang mga electron patungo sa substrate ng p-channel (dahil maitataboy ang mga singil), at hilahin ang mga butas mula sa substrate ng p-channel (yamang nakakaakit ang mga magkabilang singil).

Nakasalalay sa kung gaano kalaki ang negatibong bias VGSay, isang muling pagsasama-sama ng mga butas at electron ay nagaganap na nagreresulta sa pagbawas ng mga libreng electron sa n-channel na magagamit para sa pagpapadaloy. Ang mas mataas na antas ng negatibong bias ay nagreresulta sa mas mataas na rate ng pagsasama-sama.

Dahil dito, ang kasalukuyang alisan ng tubig ay nabawasan habang ang negatibong kundisyon sa bias ay nadagdagan, na napatunayan sa Fig.5.25 para sa VGSantas ng VGS= -1, -2 at iba pa, hanggang sa markang kurot-off ng -6V.

Ang kasalukuyang alisan ng tubig bilang isang resulta kasama ang paglipat ng plot ng curve na nalikom tulad ng isang JFET.

Ngayon, para sa positibong VGSmga halaga, positibo ang gate ay makakaakit ng labis na mga electron (libreng mga carrier) mula sa p-uri na substrate, sa account ng kasalukuyang pagtagas ng pagtulo. Ito ay magtataguyod ng mga sariwang carrier sa pamamagitan ng mga resulta ng mga banggaan sa kabuuan ng mga bumabilis na mga particle.

Tulad ng boltahe na mula sa gate-to-source ay may posibilidad na tumaas sa positibong rate, ang kasalukuyang alisan ng tubig ay nagpapakita ng isang mabilis na pagtaas, tulad ng napatunayan sa Fig.5.25 para sa parehong mga kadahilanan tulad ng tinalakay sa itaas.

Ang puwang ay nabuo sa pagitan ng mga curve ng VGS= 0V at VGS= +1 malinaw na ipinapakita ang halaga kung saan ang kasalukuyang tumaas dahil sa pagkakaiba-iba ng 1 - V ng VGS

Dahil sa mabilis na pagtaas ng kasalukuyang alisan ng tubig dapat tayong mag-ingat tungkol sa maximum na kasalukuyang rating, kung hindi man ay maaari itong tumawid sa positibong limitasyon ng boltahe ng gate.

Halimbawa, para sa uri ng aparato na nakalarawan sa Fig.5.25, paglalagay ng isang VGS= + 4V ay maaaring maging sanhi ng pagtaas ng kasalukuyang kanal sa 22.2 mA, na maaaring tumawid sa maximum na limitasyon ng breakdown (kasalukuyang) ng aparato.

Ipinapakita ng kundisyon sa itaas na ang paggamit ng isang positibong boltahe hanggang sa mapagkukunan ay bumubuo ng isang pinahusay na epekto sa dami ng mga libreng carrier sa channel, taliwas sa kung VGS= 0V.

Ito ang dahilan kung bakit ang positibong rehiyon ng boltahe ng gate sa mga katangian ng alisan o paglipat ay karaniwang kilala bilang pagpapahusay ng rehiyon . Ang rehiyon na ito ay namamalagi sa pagitan ng cut-off at antas ng saturation ng IDSSo ang rehiyon ng pagkaubos.

Paglutas ng isang Halimbawa ng Suliranin

Mga kalamangan at Aplikasyon

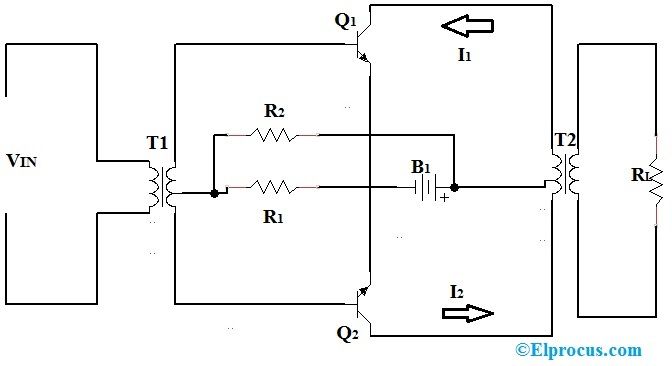

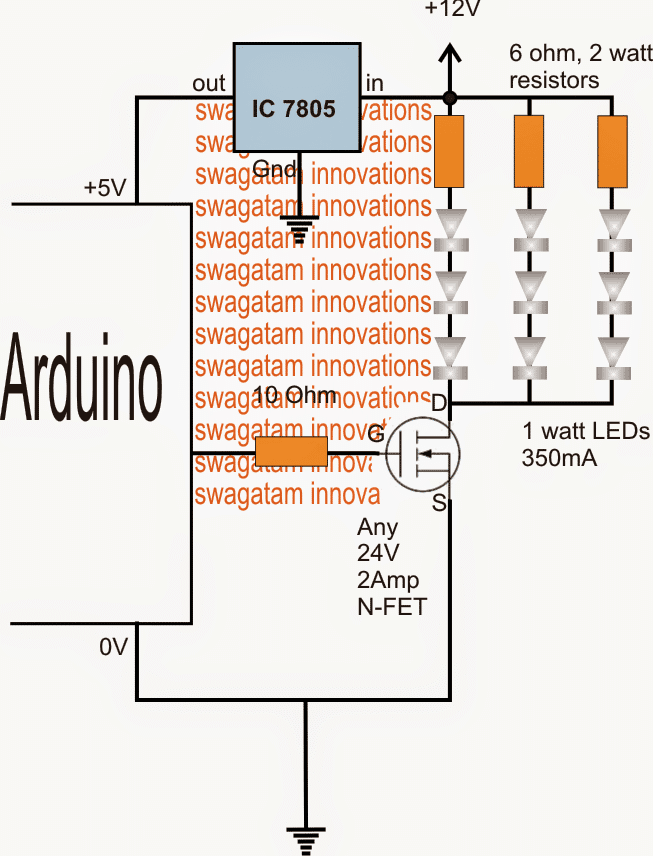

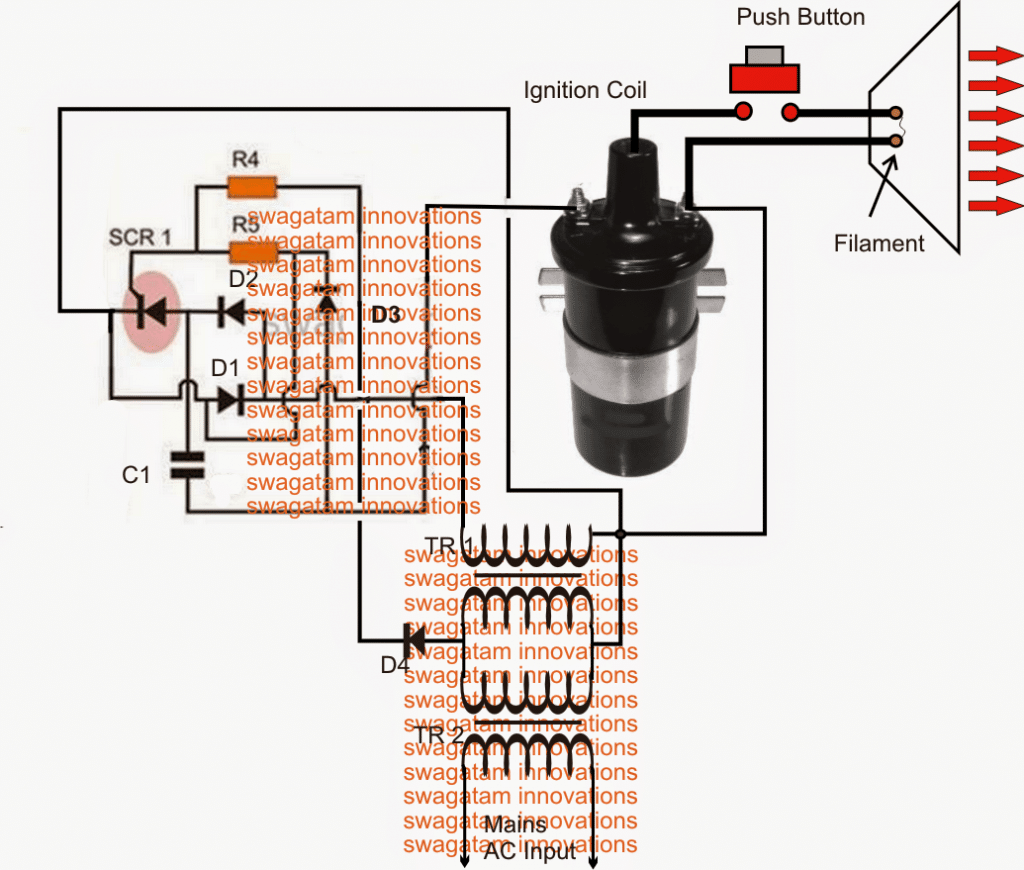

Sa kaibahan sa mga pagpapahusay na mode na MOSFET, kung saan nahahanap namin ang kasalukuyang alisan ng tubig na bumababa sa zero bilang tugon sa isang zero na gate-to-source na boltahe, ang modernong depletion-mode FET ay nagtatampok ng kapansin-pansing kasalukuyang may boltahe ng zero gate. Upang maging tumpak, ang pagtutol ng alisan ng tubig patungo sa mapagkukunan ay karaniwang 100 Ohms na zero boltahe.

Tulad ng ipinahiwatig sa nasa itaas na graph, ang ON-paglaban rds(sa)vs saklaw ng signal ng analogue ay mukhang isang patag na tugon. Ang katangiang ito, kasabay ng mga antas ng mababang kapasidad ng mga advanced na aparato ng uri ng pag-ubos, pinapayagan silang maging partikular na perpekto bilang mga switch ng analogue para sa mga application ng paglipat ng audio at video.

Ang pag-ubos na mode na MOSFET na 'normal-on' na katangian ay nagbibigay-daan sa aparato na maging perpektong angkop para sa solong mga kasalukuyang regulator ng FET.

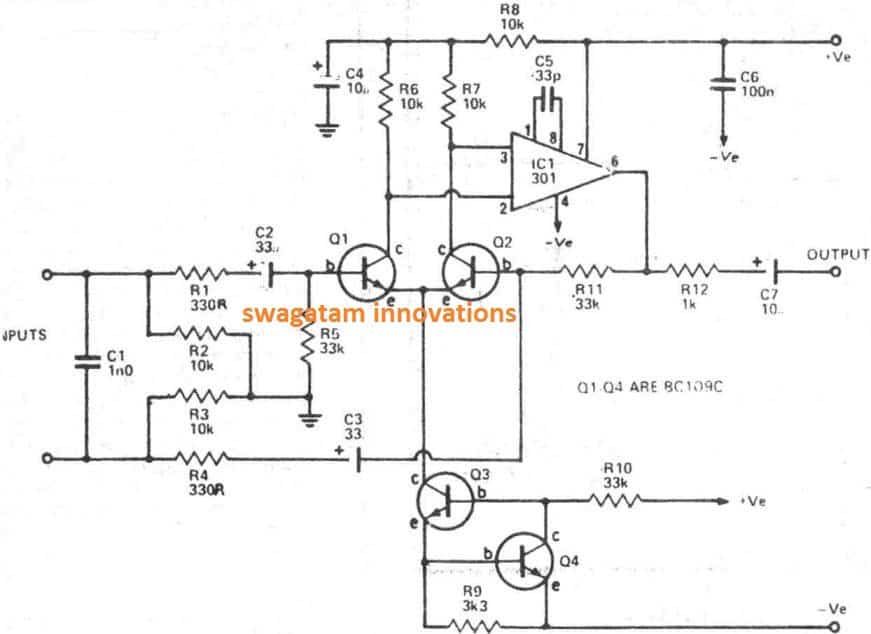

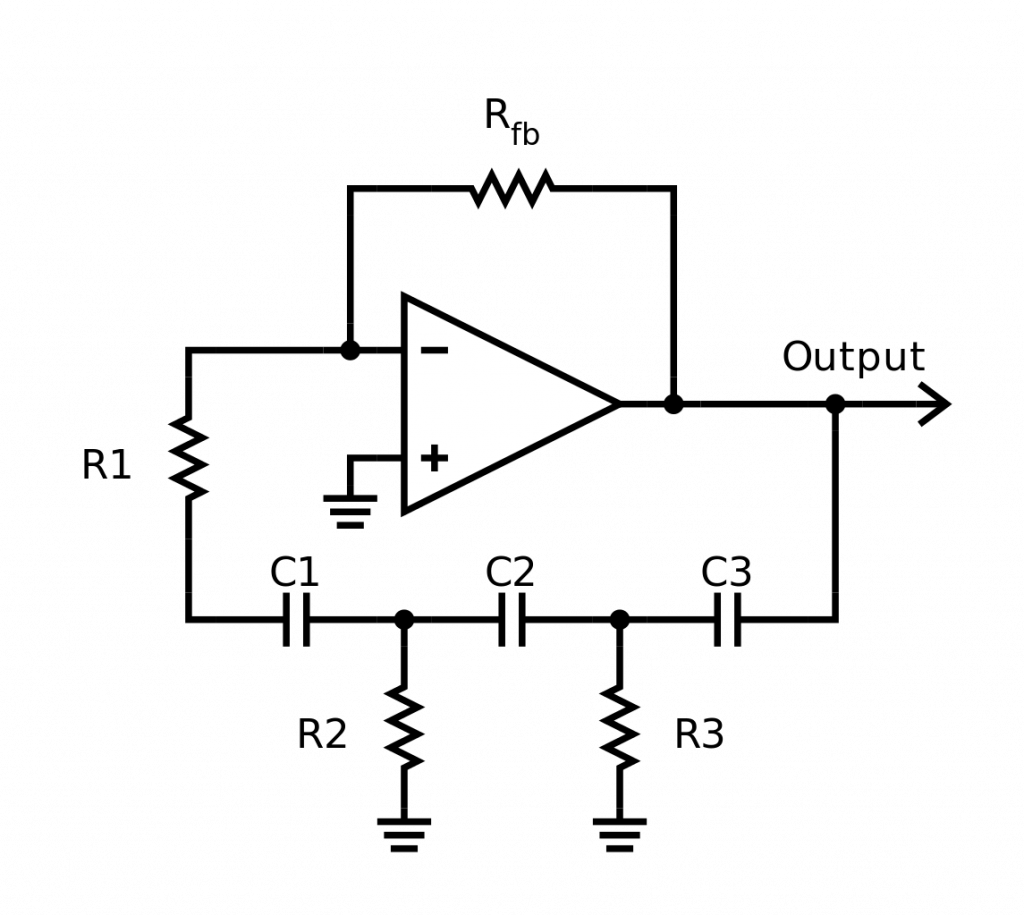

Ang isang tulad halimbawa ng circuit ay maaaring makita sa sumusunod na pigura.

Maaaring matukoy ang halaga ng Rs gamit ang formula:

Rs= VGSoff[1 - (ID/ AkoDSS)1/2] / AkoD

kung saan AkoD ay ang halaga ng kinokontrol na kasalukuyang kinakailangan sa output.

Ang pangunahing bentahe ng depletion-mode MOSFETs sa kasalukuyang application na mapagkukunan ay ang kanilang minimal na capacitance ng alisan ng tubig, na ginagawang naaangkop sa kanila para sa mga bias na aplikasyon sa low-input leakage, medium-speed (> 50 V / us) na mga circuit.

Ang pigura sa ibaba ay nagpapakita ng isang mababang-input-butas na tumutulo kasalukuyang kaugalian sa harap ng pagtapos gamit ang isang dobleng low-leakage function na FET.

Sa pangkalahatan, ang magkabilang panig ng JFET ay makiling sa ID = 500 uA. Samakatuwid, ang kasalukuyang makukuha para sa singilin ang bayad at mga stray capacitance ay nalilimitahan sa 2ID o, sa mga kasong katulad nito, 1.0 mA. Ang mga kaukulang tampok ng JFET ay napatunayan sa produksyon at tiniyak sa datasheet.

Sinasagisag ng Cs ang output capacitance ng kasalukuyang yugto ng pag-input na 'buntot'. Ang capacitance na ito ay mahalaga sa mga di-invertting amplifier, dahil sa ang katunayan na ang yugto ng pag-input ay nakakaranas ng makabuluhang mga palitan ng signal sa buong network na ito, at maaaring maging malaki ang mga pagsingil ng mga alon sa Cs. Kung sakaling ang mga kasalukuyang kasalukuyang mapagkukunan ay nagtatrabaho, ang capacitance ng buntot na ito ay maaaring managot para sa kapansin-pansin na pagkasira ng rate ng rate na hindi paikot na mga circuit (kumpara sa pag-invert ng mga application, kung saan ang pag-charge ng mga alon sa Cs ay may posibilidad na maging minimal).

Ang pagbaba ng rate ng rate ay maaaring ipahayag bilang:

1 / 1+ (Cs / Sc)

Hangga't ang Cs ay mas mababa kaysa sa Cc (ang capacitor ng kabayaran), maaaring may bahagyang pagkakaiba-iba sa rate ng pagpatay. Paggawa gamit ang DMOS FET, ang Cs ay maaaring humigit-kumulang na 2 pF. Ang diskarteng ito ay gumagawa ng isang malaking pagpapabuti sa rate ng pagpatay. Kung saan kinakailangan ang kasalukuyang mga depisit na mas mataas sa 1 hanggang 5 mA, ang aparato ay maaaring makiling sa mode ng pagpapahusay upang makabuo ng hanggang 20 mA para sa isang maximum na VGS na +2.5 V, na may kaunting output capacitance na patuloy na isang pangunahing aspeto.

Ang susunod na application sa ibaba ay nagpapakita ng wastong pagpapahusay-mode na kasalukuyang circuit ng pinagmulan.

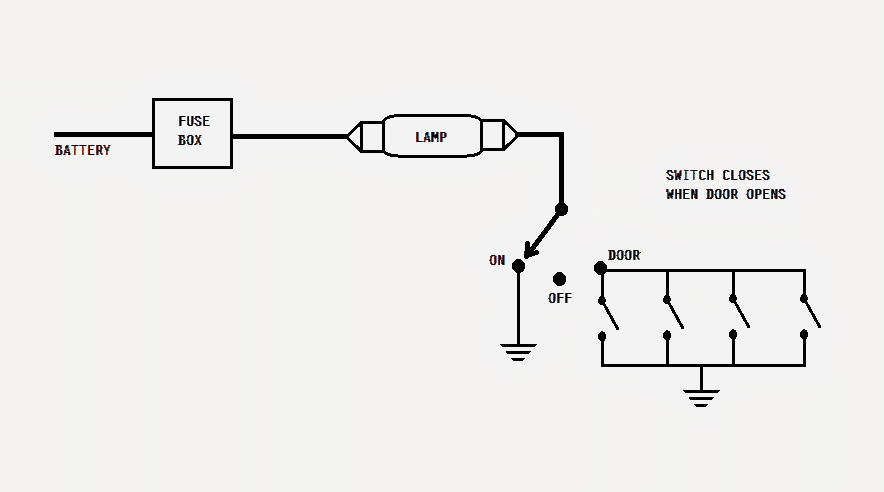

Ang isang 'normal -on' analogue switch ay maaaring itayo para sa mga kinakailangan kung saan kinakailangan ang karaniwang kondisyon sa panahon ng pagkabigo ng boltahe ng supply, halimbawa sa awtomatikong pagsasama ng mga tool sa pagsubok o para matiyak ang tumpak na pagsisimula ng mga circuit ng lohika sa ON ON.

Ang pinababang negatibong boltahe ng threshold ng aparato ay nag-aalok ng pangunahing mga kinakailangan sa pagmamaneho at pinahihintulutan ang pagtatrabaho na may kaunting boltahe.

Ipinapakita ng circuit sa ibaba ang karaniwang mga kadahilanan ng bias para sa anumang depletion-mode DMOS analogue switch.

Upang magawang patayin ang aparato, kinakailangan ng isang negatibong boltahe sa gate. Na sinabi na, ang on-paglaban ay maaaring mabawasan kapag ang FET ay karagdagang pinahusay na gamit ang isang positibong boltahe ng gate, partikular na pinapagana ang rehiyon ng pagpapahusay-mode kasama ang pag-ubos ng rehiyon na -mode.

Ang tugon na ito ay maaaring masaksihan sa sumusunod na grap.

Ang mataas na dalas na nakuha ng yunit, kasama ang mga mababang halaga ng capacitance, ay naghahatid ng isang nadagdagan na 'pigura ng merito'. Talagang ito ay isang mahalagang elemento sa VHF at UHF amplification, na tumutukoy sa produkto ng gain-bandwidth (GBW) ng FET, na maaaring mailarawan bilang:

GBW = gfs / 2 Pi (Csa+ Cpalabas)

p-Channel Depletion-Type MOSFET

Ang pagtatayo ng isang p-channel depletion-type MOSFET ay isang perpektong baligtad ng isang n-channel na bersyon na ipinakita sa Fig.5.23. Ibig sabihin, ang substrate ngayon ay kumukuha ng form ng isang n-type at ang channel ay nagiging isang p-type, tulad ng makikita sa Fig.5.28a sa ibaba.

Ang pagkakakilanlan ng terminal ay mananatiling hindi nagbabago, ngunit ang boltahe at ang kasalukuyang polarities ay baligtad, tulad ng ipinahiwatig sa parehong pigura. Ang mga katangian ng alisan ng tubig ay eksaktong eksaktong inilalarawan sa Fig.5.25, maliban sa VDSmag-sign kung alin sa kasong ito ay makakakuha ng isang negatibong halaga.

Ang kasalukuyang kanal IDnagpapakita ng isang positibong polarity sa kasong ito din, iyon ay dahil nabaligtad na namin ang direksyon nito. VGSay nagpapakita ng isang kabaligtaran polarity, na kung saan ay naiintindihan, tulad ng ipinahiwatig sa Fig.5.28c.

Dahil VGSAng baligtad ay gumagawa ng isang imahe ng salamin para sa mga katangian ng paglipat tulad ng ipinahiwatig sa Fig.5,28b.

Ibig sabihin, tumataas ang kasalukuyang alisan ng tubig sa positibong VGSrehiyon mula sa cut-off point sa VGS= Vp hanggang sa akoDSS, pagkatapos ay patuloy itong tumaas bilang negatibong halaga ng VGStumataas

Mga Simbolo

Ang mga graphic na palatandaan para sa isang n- at p-channel na pag-ubos na uri ng MOSFET ay maaaring masaksihan sa itaas ng Larawan 5.29.

Pagmasdan ang paraan ng layunin ng mga napiling simbolo na kumatawan sa totoong istraktura ng aparato.

Ang kawalan ng isang direktang koneksyon (dahil sa pagkakabukod ng gate) sa pagitan ng gate at channel ay sinasagisag ng isang agwat sa pagitan ng gate at ng iba't ibang mga terminal ng simbolo.

Ang patayong linya na kumakatawan sa channel ay nakakabit sa pagitan ng alisan ng tubig at mapagkukunan at 'hinawakan' ng substrate.

Dalawang pangkat ng mga simbolo ang ibinigay sa figure sa itaas para sa bawat uri ng channel upang i-highlight ang katotohanan na sa ilang mga aparato ang substrate ay maaaring ma-access sa labas habang sa iba ay maaaring hindi ito makita.

MOSFET (Uri ng Pagpapahusay)

Bagaman ang uri ng pag-ubos at uri ng pagpapahusay na mga MOSFET ay magkatulad sa kanilang panloob na mga istraktura at pag-andar na mode, ang kanilang mga katangian ay maaaring magkakaiba.

Ang pangunahing pagkakaiba ay ang kasalukuyang alisan ng tubig na nakasalalay sa isang tukoy na antas ng boltahe hanggang sa mapagkukunan para sa cut-off na aksyon.

Tiyak na, ang isang uri ng pagpapahusay na uri ng n-channel na MOSFET ay maaaring gumana kasama ang isang positibong boltahe / pinagmulan ng mapagkukunan, sa halip na isang saklaw ng mga negatibong potensyal na maaaring makaapekto sa isang uri ng pag-ubos ng MOSFET.

Pangunahing Konstruksyon

Maaari mong mailarawan ang uri ng pagpapahusay na uri ng n-channel na MOSFET sa mga sumusunod

Larawan 5.31.

Ang isang seksyong materyal na uri ng p ay nilikha sa pamamagitan ng isang base ng silikon, at tulad ng natutunan bago ito tinawag bilang substrate.

Ang substrate na ito sa ilang mga okasyon ay nakakabit sa panloob na may pin na mapagkukunan sa isang uri ng pag-ubos na MOSFET, habang sa ilang mga pagkakataon ay winakasan ito bilang isang ika-apat na lead para sa pagpapagana ng isang panlabas na kontrol ng potensyal na antas nito.

Ang mga terminal ng mapagkukunan at alisan ng tubig ay tulad ng dati na sumali gamit ang mga metal na contact sa mga n-doped na rehiyon.

Gayunpaman, maaaring mahalaga na mailarawan na sa Larawan 5.31 ang channel sa pagitan ng dalawang mga n-doped na rehiyon ay nawawala.

Maaari itong isaalang-alang bilang pangunahing pangunahing pagkakaiba sa pagitan ng isang uri ng pag-ubos at isang panloob na layout ng MOSFET na uri ng pagpapahusay, iyon ay isang kawalan ng isang likas na channel na kung saan ay dapat na isang bahagi ng aparato.

Ang layer ng SiO2 ay makikita pa ring laganap, na tinitiyak ang isang paghihiwalay sa pagitan ng metal na base ng terminal ng gate at ng rehiyon sa pagitan ng kanal at mapagkukunan. Gayunpaman, dito masasaksihan ang nakatayo na hiwalay mula sa seksyong p-uri ng materyal.

Mula sa talakayan sa itaas maaari nating tapusin na ang isang pag-ubos at pagpapahusay ng panloob na layout ng MOSFET ay maaaring magkaroon ng ilang pagkakatulad, maliban sa nawawalang channel sa pagitan ng alisan ng tubig / mapagkukunan para sa isang pagpapahusay na uri ng MOSFET.

Pangunahing Pagpapatakbo at Mga Katangian

Para sa isang uri ng pagpapahusay na MOSFET kapag ang isang 0 V ay ipinakilala sa VGS nito, dahil sa nawawalang n-channel (na kilalang nagdadala ng maraming mga libreng carrier) ay nagiging sanhi ng isang kasalukuyang output na zero, na medyo hindi katulad ng isang uri ng pag-ubos ng MOSFET, pagkakaroon ng ID = IDSS.

Sa ganitong sitwasyon dahil sa isang nawawalang landas sa mga drain / source terminal, maraming halaga ng mga carrier sa anyo ng mga electron ay hindi maipon sa drain / source (dahil sa mga n-doped na rehiyon).

Ang paglalapat ng ilang positibong potensyal sa VDS, na ang VGS ay nakatakda sa zero volts at ang terminal ng SS na pinaikling may mapagkukunang terminal, talagang nakita namin ang isang pares ng reverse bias na pn junction sa pagitan ng mga n-doped na rehiyon at ng p-substrate upang paganahin ang anumang kilalang konduksyon sa kabuuan alisan ng tubig patungo sa mapagkukunan.

Sa Fig. 5.32 ay nagpapakita ng isang kundisyon kung saan ang VDS at VGS ay inilalapat na may ilang positibong boltahe na mas mataas sa 0 V, na pinapayagan ang alisan ng tubig at gate na maging isang positibong potensyal na patungkol sa mapagkukunan.

Ang positibong potensyal sa gate ay itinutulak ang mga butas sa p-substrate kasama ang gilid ng layer ng SiO2 na umaalis sa lokasyon at papasok ng mas malalim sa mga rehiyon ng p-substrate, tulad ng ipinakita sa itaas na pigura. Nangyayari ito dahil sa mga katulad na pagsingil na nagtataboy sa bawat isa.

Nagreresulta ito sa isang rehiyon ng pagkaubos na nilikha malapit sa layer ng pagkakabukod ng SiO2 na walang bisa ng mga butas.

Sa kabila nito, ang mga p-substrate electron na kung saan ay ang mga minorya na nagdadala ng materyal ay hinila patungo sa positibong gate at magsimulang magtipon sa rehiyon na malapit sa ibabaw ng layer ng SiO2.

Dahil sa pagkakabukod ng pag-aari ng SiO2 layer na mga negatibong carrier ay pinapayagan ang mga negatibong carrier mula sa masipsip sa terminal ng gate.

Habang pinapataas namin ang antas ng VGS, ang density ng electron na malapit sa ibabaw ng SiO2 ay tumataas din, hanggang sa wakas na ang sapilitan n-uri na rehiyon ay pinapayagan ang isang nabibilang na pagpapadaloy sa buong kanal / mapagkukunan.

Ang lakas na VGS na nagdudulot ng isang pinakamainam na pagtaas sa kasalukuyang kanal ay tinawag bilang boltahe ng threshold, signified ng simbolo VT . Sa mga datasheet makikita mo ito bilang VGS (Th).

Tulad ng natutunan sa itaas, dahil sa kawalan ng isang channel sa VGS = 0, at 'pinahusay' na may positibong gate-to-source voltage application, ang ganitong uri ng MOSFET ay kilala bilang mga MOSFET na uri ng pagpapahusay.

Malalaman mo na ang parehong pag-ubos at uri ng pagpapahusay na mga MOSFET ay nagpapakita ng mga rehiyon na uri ng pagpapahusay, ngunit ang term na pagpapahusay ay ginagamit para sa huli dahil partikular itong gumagana gamit ang isang pagpapahusay na mode ng operasyon.

Ngayon, kapag ang VGS ay itinulak sa halaga ng threshold, ang konsentrasyon ng mga libreng carrier ay magpapalakas sa channel kung saan ito sapilitan. Ito ay sanhi ng pagtaas ng kasalukuyang kanal.

Sa kabilang banda, kung panatilihin natin ang VGS na pare-pareho at taasan ang antas ng VDS (boltahe na mapagkukunan ng tubo), sa huli ito ay magiging sanhi ng MOSFET na maabot ang punto ng saturation nito, tulad ng karaniwang mangyayari sa anumang JFET o isang pag-ubos ng MOSFET.

Tulad ng ipinakita sa Larawan 5.33 ang kasalukuyang kanal ng ID ay na-level up sa tulong ng isang proseso ng pag-pinch-off, na ipinahiwatig ng mas makitid na channel patungo sa dulo ng kanal ng sapilitan na channel.

Sa pamamagitan ng paglalapat ng batas ng boltahe ng Kirchhoff sa mga voltages ng terminal ng MOSFET sa Larawan 5.33, nakukuha natin:

Kung ang VGS ay pinananatiling pare-pareho sa isang tukoy na halaga, halimbawa 8 V, at ang VDS ay itinaas mula 2 hanggang 5 V, ang boltahe VDG ng Eq. Makikita ang 5.11 na bumababa mula -6 hanggang -3 V, at ang potensyal na gate ay nakakakuha ng mas kaunti at mas positibong patungkol sa boltahe ng alulod.

Ipinagbabawal ng tugon na ito ang mga libreng carrier o electron mula sa paghila papunta sa rehiyon na ito ng sapilitan na channel, na kung saan ay magreresulta sa isang pagbagsak sa mabisang lapad ng channel.

Sa huli, ang lapad ng channel ay bumababa sa punto ng kurot-off, na umaabot sa isang kondisyon ng saturation na katulad ng natutunan na sa aming naunang pag-ubos na artikulo ng MOSFET.

Ibig sabihin, ang pagdaragdag ng VDS ng anumang karagdagang gamit ang isang nakapirming VGS ay hindi nakakaapekto sa antas ng saturation ng ID, hanggang sa puntong naabot ang isang sitwasyon ng pagkasira.

Sa pagtingin sa Fig 5.34 maaari nating makilala na para sa isang MOSFET tulad ng sa Fig.5.33 pagkakaroon ng VGS = 8 V, ang saturation ay nagaganap sa antas ng VDS na 6 V. Upang maging tumpak na ang antas ng saturation ng VDS ay nauugnay sa inilapat na antas ng VGS ng:

Walang alinlangan, sa gayon ito ay nagpapahiwatig na kapag ang halaga ng VT ay naayos, ang pagtaas ng antas ng VGS ay proporsyonal na magiging sanhi ng mas mataas na antas ng saturation para sa VDS sa pamamagitan ng lokasyon ng mga antas ng saturation.

Sumangguni sa mga katangiang ipinakita sa nasa itaas na pigura, ang antas ng VT ay 2 V, na maliwanag sa pamamagitan ng ang katunayan na ang kasalukuyang alisan ng tubig ay bumagsak sa 0 mA.

Samakatuwid karaniwang maaari nating sabihin:

Kapag ang mga halaga ng VGS ay mas mababa sa antas ng threshold para sa uri ng pagpapahusay na MOSFET, ang kasalukuyang alisan ng tubig nito ay 0 mA.

Malinaw din nating nakikita ang nasa itaas na pigura na hangga't ang VGS ay itinaas nang mas mataas mula sa VT hanggang 8 V, ang katumbas na antas ng saturation para sa ID ay tumataas din mula 0 hanggang 10 mA na antas.

Bukod dito maaari pa nating mapansin na ang puwang sa pagitan ng mga antas ng VGS ay tumataas sa isang pagtaas sa halaga ng VGS, na nagdudulot ng isang walang katapusang pagtaas ng mga pagtaas sa kasalukuyang alisan ng tubig.

Nalaman namin na ang kasalukuyang halaga ng alisan ng tubig ay nauugnay sa boltahe ng gate-to-source para sa mga antas ng VGS na mas malaki kaysa sa VT, sa pamamagitan ng sumusunod na relasyon na hindi linya:

Ang term na ipinakita na may parisukat na bracket ay ang term na responsable para sa hindi linya na relatinship sa pagitan ng ID at VGS.

Ang term na k ay isang pare-pareho at isang pagpapaandar ng layout ng MOSFET.

Malalaman natin ang halaga ng pare-pareho na k sa pamamagitan ng sumusunod na equation:

kung saan ang ID (on) at VGD (on) bawat isa ay partikular na mga halaga depende sa katangian ng aparato.

Sa susunod na Larawan 5.35 sa ibaba matatagpuan namin ang alisan ng tubig at ang mga katangian ng paglipat ay nakaayos ng isa sa tabi ng isa pa upang linawin ang proseso ng paglipat sa isa't isa.

Talaga, ito ay katulad ng proseso na ipinaliwanag dati para sa JFET at mga deportion na uri ng MOSFET.

Gayunpaman, para sa kasalukuyang kaso kailangan nating tandaan na ang kasalukuyang alisan ng tubig ay 0 mA para sa VGS VT.

Dito maaaring makakita ang ID ng isang kapansin-pansin na halaga ng kasalukuyang, na tataas na tinutukoy ng Eq. 5.13.

Tandaan, habang tinutukoy ang mga puntos sa mga katangian ng paglipat mula sa mga katangian ng alisan ng tubig, isinasaalang-alang lamang namin ang mga antas ng saturation. Pinaghihigpitan nito ang rehiyon ng operasyon sa mga halagang VDS na mas mataas kaysa sa mga antas ng saturation na itinatag ng Eq. (5.12).

p-Channel Pagpapahusay-Uri MOSFETs

Ang istraktura ng isang p-channel na pagpapahusay na uri ng MOSFET tulad ng ipinakita sa Larawan 5.37a ay kabaligtaran lamang ng na ipinapakita sa Larawan 5.31.

Ibig sabihin,, ngayon nalaman mo na ang isang n-type na substrate at mga p-doped na rehiyon sa ilalim ng kanal at pinagmulan ng mga kasukasuan.

Ang mga terminal ay patuloy na itinatag, ngunit ang bawat isa sa mga kasalukuyang direksyon at ang boltahe polarities ay baligtad.

Ang mga katangian ng alisan ng tubig ay maaaring magmukhang naibigay sa Larawan 5.37c, pagkakaroon ng pagtaas ng halaga ng kasalukuyang sanhi ng isang patuloy na mas negatibong lakas ng VGS.

Ang mga katangian ng paglipat ay magiging impression ng mirror (sa paligid ng axis ng ID) ng curve ng paglipat ng Larawan 5.35, pagkakaroon ng pagtaas ng ID na may higit at mas maraming mga negatibong halaga ng VGS sa itaas ng VT, tulad ng ipinakita sa Larawan 5.37b. Ang mga equation (5.11) hanggang (5.14) ay katulad na naaangkop sa mga aparatong p-channel.

Mga Sanggunian:

- https://en.wikipedia.org/wiki/MOSFET

- https://hi.wikipedia.org/wiki/%E0%A4 %AE%E0 %A5 %89%E0%A4 %B8%E0 %A4 %AB %E0 %A5%87%E0%A4 %9F

Nakaraan: Anti Spy RF Detector Circuit - Wireless Bug Detector Susunod: Mga Katangian sa Paglipat